Information Technology Reference

In-Depth Information

ware-Software-Codesign eines Prozessors jedoch Erweiterungen vornehmen, die

eine ausreichend schnelle Interpretation in Hardware möglich machen. Zum Bei-

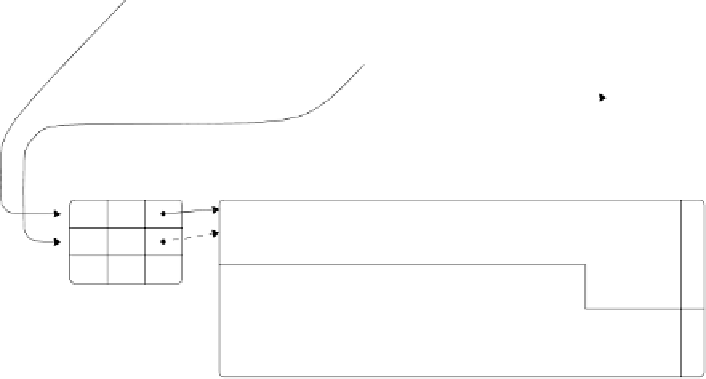

spiel ließen sich die virtuellen Nemesis-Befehle in Bild 4.9 mikroprogrammiert

emulieren, wobei das Laufzeitprofil automatisch in einem Zähler-Cache, ähnlich

wie er in Daisy von IBM realisiert ist [34, 35, 36], erstellt werden könnte. Im Ver-

gleich zu einem die sequentiellen Nemesis-Befehle direkt ausführenden realen Pro-

zessor, wie dem Nemesis C, müssten Geschwindigkeitsnachteile hierbei nicht in

Kauf genommen werden

1

.

Nemesis-Befehlsfolge

1:

sub

r0, r0, 1

2: L1:

sub

r1, r2, r3

3:

add

r4, r1, r7

4:

and.cr0

r7, r8, r9

5:

bne

L2

7: L2:

xor

r1, r2, r3

6:

orn

r2, r2, -1

8:

cmp

r7', r8

9:

bhi

L3

10:

sub.cr0

r2, r2, 1

11:

beq

L1

Trace-Cache

Trace-Buffer-Eintrag (Nemesis-X-Befehlsfolge)

1: V1:

sub

r1, r2, r3;

and.cr0

r7', r8, r9;;

L1

3

2: V4:

add

r4, r1, r7;

xor'

r1', r2, r3

beq

V2;;

•

L2

2

3:

cmp

r7', r8;

sub.cr0'

r2', r2, 1;;

4:

set

r1 | r7;

bhi

V3;;

5:

set

cr0 | r2;

beq

V1;;

6:

stop

...;;

7: V2:

set

r7;

stop

...;;

8: V3:

stop

L3;;

Bild 4.9.

Umsetzung einer sequentiellen virtuellen Nemesis-Befehlsfolge in eine reale operations-

parallele Befehlsfolge für die VLIW-Architektur Nemesis X

Ein weiterer Parameter, der die Ausführungsgeschwindigkeit eines Programms in

der hier beschriebenen Weise beeinflusst, ist der Grenzwert, den die bei der Profiler-

stellung verwendeten Zähler überschreiten müssen, damit die virtuelle Befehlsfolge

durch Binärübersetzung in eine operationsparallele reale Befehlsfolge umgesetzt

wird. Ein zu klein gewählter Grenzwert führt dazu, dass die zeitaufwendige dynami-

sche Binärübersetzung mit virtuellen Befehlsfolgen durchgeführt wird, die nur sel-

ten zur Ausführung kommen, ein zu groß gewählter Grenzwert, dass häufig bearbei-

tete virtuelle Befehlsfolgen, z.B. Schleifen, unnötig lange interpretiert werden.

Letztendlich lässt sich der Grenzwert nur nichtkausal als Funktion der Zeiten für die

sequentielle Interpretation, für die Binärübersetzung und für die endgültige Bearbei-

tung einer virtuellen bzw. realen Befehlsfolge berechnen. Dies müsste für jede virtu-

1.

Aus Komplexitätsgründen sind die in Nemesis X für die Interpretation von virtuellen Nemesis-

Befehlen vorgesehenen Erweiterungen etwas einfacher gehalten. So verfügt Nemesis X über

einen Befehl fetch, mit dem der nächste zu interpretierende Befehl geholt und decodiert werden

kann, und einen zweiten Befehl interpr, der abhängig vom zuvor extrahierten und in einem Spe-

zialregister abgelegten Operationscode eine VLIW-Befehlsfolge aufruft.

Search WWH ::

Custom Search