Information Technology Reference

In-Depth Information

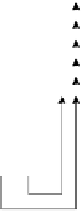

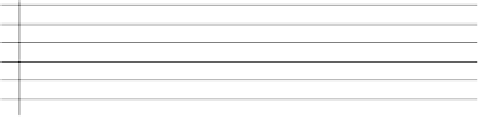

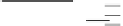

Registerspeicher sind drei Verarbeitungseinheiten dargestellt, die je nach angestreb-

ter Leistungsfähigkeit ggf. auch mehrfach implementiert sein können (für Register-

speicher, ALU und Speicherzugriffseinheit MEM ist das als Schatten angedeutet).

Befehls-

speicher

+1

c

IR

e

a

Reg

Const

BPU

ALU

MEM

d

b

addr

data

Bild 3.29.

Prozessor mit kontrollflussgesteuertem Datenfluss. Pro Takt können bis zu sechs Trans-

portoperationen ausgeführt werden

Ähnlich wie bei den meisten Kontrollflussprozessoren wird in einem ersten Schritt

der zu verarbeitende Befehl aus dem Befehlsspeicher in das mit a markierte Instruk-

tionsregister IR geladen (die Anbindung des Befehlsspeichers ist der Einfachheit

halber ohne die normalerweise vorhandene Speicherverwaltungseinheit, den Cache,

eine Sprungvorhersageeinheit und eine Einheit zum Lesen variabel breiter Befehle

dargestellt). Die im Befehl codierten sechs Transportoperationen enthalten je zwei

Adressen zur Auswahl einer Quelle und einer Senke, die bei Ausführung über einen

der Transportoperation fest zugeordneten Bus miteinander verbunden werden. So ist

in Bild 3.29 z.B. - stark ausgezogen und mit b markiert - dargestellt, wie sich der

Inhalt eines Registers zum linken Eingang der ALU transportieren lässt. Welches

Register dabei gelesen wird, ist in der Quelladresse der entsprechenden Transporto-

peration festgelegt. Ebenso muss in der Zieladresse ggf. codiert sein, welche Opera-

tion von der ALU bearbeitet werden soll. Bei Ausführung mehrstelliger Operationen

ist dies jedoch nur mit der Adresse eines einzelnen, z.B. des am weitesten links ste-

henden Operanden erforderlich.

Die Bearbeitung einer Operation beginnt, sobald alle benötigten Operanden verfüg-

bar sind, d.h. am Ende der Ausführung des Befehls, mit dem der letzte Operand zur

jeweiligen Verarbeitungseinheit transportiert wird. Im günstigsten Fall steht das

erzeugte Ergebnis einen Takt später am Ausgang der Verarbeitungseinheit bereit.

Dies bedeutet jedoch nicht, dass es unmittelbar im nächsten Takt gelesen werden

muss, da es ggf. in einem Ringpuffer (FiFo) zwischengespeichert wird (im Bild zur

ALU mit d markiert). Dabei sind drei Sonderfälle zu berücksichtigen:

1. Ein ähnliches Konzept ist mit ADARC in [169, 59] beschrieben. Der zu verarbeitende Daten-

fluss wird jedoch nicht durch eine Folge von Transportoperationen, wie im vorliegenden Fall,

sondern durch in 3-Adressoperationen codierte Kennungen formuliert. Abhängigkeiten werden

gelöst, indem man die Kennungen der zu konsumierenden Operanden mit denen der erzeugten

Ergebnisse vergleicht und bei Übereinstimmung mit Hilfe eines assoziativen Kommunikations-

netzes eine Verbindung zwischen den entsprechenden Verarbeitungseinheit herstellt.

Search WWH ::

Custom Search