Information Technology Reference

In-Depth Information

bereits mit dem Vergleich feststehen muss, welche Bedingung auszuwerten ist. Falls

zwei Operanden entsprechend unterschiedlicher Relationen verglichen werden, sind

demzufolge mehrere Vergleichsoperationen erforderlich. Die meisten Prozessoren

erzeugen mit einem Vergleich deshalb nicht ein einzelnes Bedingungsbit entspre-

chend einer bestimmten Relation, sondern einen Bedingungscode entsprechend aller

von einem Prozessor auswertbaren Relationen und speichern das Ergebnis entweder

in einem allgemein verwendbaren Register oder in einem meist als Bedingungsre-

gister bezeichneten Spezialregister. Anders als bei den in vorangehenden Abschnit-

ten beschriebenen Zahlentypen ist dabei die Anordnung der Bedingungsbits von

geringer Bedeutung und oft vom Prozessorhersteller willkürlich festgelegt.

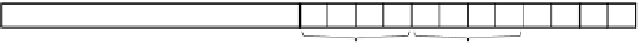

Ein Prozessor, bei dem der Bedingungscode in einem allgemein verwendbaren

Register gespeichert wird, ist der mittlerweile nicht mehr gefertigte RISC-Prozessor

MC88100 von Motorola [122], der mit einem Vergleich 10 Bedingungsbits parallel

erzeugt und als 32 Bit breiter Bedingungscode entsprechend Bild 1.6 codiert.

Beachtenswert ist, dass geordnete Relationen, also „kleiner“, „größer“, „kleiner

gleich“ und „größer gleich“ jeweils für vorzeichenbehaftete Zahlen und vorzeichen-

lose Zahlen erzeugt werden, was deshalb erforderlich ist, weil die notwendige

Unterscheidung nicht mit dem Vergleich erfolgt.

31

0

00...0

hs

lo

ls

hi

ge

lt

le

gt

ne

eq

0

0

Unsigned

Signed

=

b ist (equal)

eq:

ne:

nur gesetzt, wenn a

≠

b ist (not equal)

nur gesetzt, wenn a

>

b ist (greater than)

gt:

le:

lt:

ge:

nur gesetzt, wenn a

≤

b ist (less than or equal)

nur gesetzt, wenn a

Vorzeichenbehaftet

(signed)

<

nur gesetzt, wenn a

b ist (less than)

≥

nur gesetzt, wenn a

b ist (greater than or equal)

>

b ist (higher than)

hi:

ls:

lo:

hs:

nur gesetzt, wenn a

≤

b ist (lower than or same)

nur gesetzt, wenn a

Vorzeichenlos

(unsigned)

<

b ist (lower than)

nur gesetzt, wenn a

≥

b ist (higher than or same)

nur gesetzt, wenn a

Bild 1.6.

32 Bit breiter Bedingungscode im MC88100 von Motorola [122]

Beispiel 1.3.

Rechnen mit Bedingungen (MC88100)

. Die Codierung von 10 Bedingungsbits in

einem 32-Bit-Wort entsprechend Bild 1.6 hat den Vorteil, dass ähnlich wie beim Itanium, dem

Alpha 21364 und dem DLX einzelne Bedingungen logisch miteinander verknüpft werden können.

Sie müssen hierzu nur durch Schiebeoperationen nach Bedarf ausgerichtet werden. Um z.B. die

Bedingung a = b UND c ≠ d zu berechnen, kann zunächst a und b sowie c und d einzeln verglichen,

anschließend der Bedingungscode z.B. des ersten Vergleichs um eine Position nach links verscho-

ben und das Ergebnis schließlich mit dem Bedingungscode des zweiten Vergleichs durch bitweises

UND verknüpft werden. Die Schiebeoperation ist erforderlich, um die Bedingungsbits eq des ersten

Vergleichs und ne des zweiten Vergleichs untereinander anzuordnen, weshalb hier die Verknüpfung

von Bedingungen i.Allg. langsamer ist, als wäre ein wahlfreier Zugriff auf Bedingungsbits mög-

Search WWH ::

Custom Search