Information Technology Reference

In-Depth Information

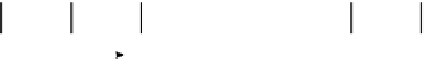

onen und Verarbeitungseinheiten ist beim drei Operationen enthaltenden

Befehlsformat fest definiert. Beim zwei Operationen enthaltenden Befehlsformat

geschieht sie derart, dass die 22 Bit breite Operation OP1 fest einer einzelnen

Verarbeitungseinheit und die 42 Bit breite Operation OP2 alternativ von einer

der beiden verbleibenden Verarbeitungseinheiten ausgeführt wird.

Neben der einfachen Realisierung ist das für VLIW-Prozessoren ausgesprochen

kompakte Befehlsformat von Vorteil. Während z.B. der Nemesis X im Idealfall

12 Operationen in einem 256 Bit umfassenden Bereich codieren kann, sind dies

acht Operationen beim TMS320C62x von Texas Instruments, einem Prozessor,

der ebenfalls ein sehr kompaktes Befehlsformat aufweist [185]. Allerdings

besteht dieser Vorteil nur, wenn es möglich ist, wenigstens zwei sinnvolle Opera-

tionen in einem Befehl zu codieren.

Prozessor aus Bild 3.13

AL

FP

BR

a

Trace 7/300*)

mask

OP4

OP3

OP2

OP1

256

256

0

0

AL1

BR

AL2

AL3

AL4

FP1

FP2

b

Nemesis X

63

42

20

0

OP1

OP2

OP3

OP1

OP2

c

TM-1300*)

219

0

fm

fm

fm

fm

fm

OP1

OP2

OP3

OP4

OP5

d

TMS320C62x

256

224

192

160

128

96

64

32

0

OP1

P

OP2

P

OP3

P

OP4

P

OP5

P

OP6

P

OP7

P

OP8

P

e

0

1

1

0

0

1

1

x

IA-64 (Itanium)

127

87

46

5

4

0

OP3

OP2

OP1

temp

l.

f

Bild 3.15.

Befehlsformate gängiger VLIW-Prozessoren. *) Die bitgenauen Aufteilungen der

Befehle des Trace 7/300 von Multiflow und des TM-1300 von Philips sind dem Autor unbekannt.

Die Teilbilder b und d sind daher als grundsätzlich zu verstehen (vgl. [101] und [39])

Search WWH ::

Custom Search