Information Technology Reference

In-Depth Information

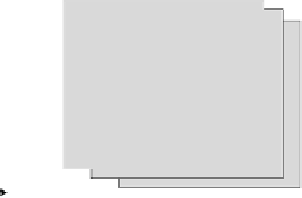

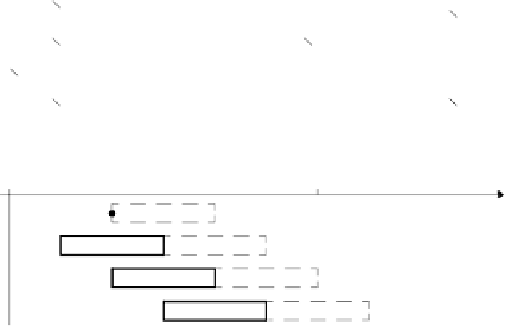

Außerdem muss die Anzahl der Speicherbänke größer oder gleich der Anzahl der

hintereinander geschalteten Register sein, damit über längere Zeiträume ein Durch-

satz von einem gelesenen Datum pro Takt erreicht werden kann.

b

strobe

Controller

wait

d

a

c

write

data in

data out

M

1

Bank 0

D

1

addr

2

e

f

a

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

basis + 0

Bank 2

basis + 1

Bank 3

Bank 0

basis + 2

basis + 3

Bank 1

b

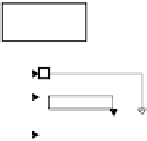

Bild 3.7.

Vierfach verschränkter Speicher.

a

Registertransferschaltung einer möglichen Realisie-

rung.

b

Zeitlicher Ablauf einer Zugriffsfolge mit aufeinander folgenden Adressen

Der zeitliche Ablauf bei Zugriffen auf verschränkten Speicher entsprechend Bild

3.7a mit unmittelbar aufeinander folgenden Wortadressen ist in Bild 3.7b darge-

stellt. Nach dem ersten Zugriff auf Speicherbank 2 kann trotz der Latenzzeit von

hier angenommenen zwei Takten bereits einen Takt später, nämlich zum Zeitpunkt

t

1

, mit der inkrementierten Adresse basis+1 auf Speicherbank 3 zugegriffen werden.

Im Prinzip könnte sich der Zugriff auch auf die Speicherbänke 0 oder 1 beziehen, da

lediglich Speicherbank 2 durch den zuvor gestarteten Zugriff blockiert ist.

Unter den gegebenen Voraussetzungen ist es also möglich, jede Adressfolge verzö-

gerungsfrei zu bearbeiten, die die Eigenschaft hat, dass zwei aufeinander folgende

Zugriffe sich nicht auf dieselbe Speicherbank beziehen. Statt die Adresse also

jeweils um 1 zu inkrementieren, könnte sie auch um 2, 3, 5, 6 oder allgemein um

jede Schrittweite inkrementiert werden, die in den unteren beiden Bits ungleich 00

2

ist. Die Verhältnisse ändern sich, wenn die Latenzzeit eines einzelnen Speicherzu-

griffs statt zwei z.B. vier Takte beträgt, was in Bild 3.7b als gestrichelte Balken dar-

gestellt ist. In diesem Fall ist eine Adressfolge nur dann verzögerungsfrei bear-

beitbar, wenn sich die letzten vier Zugriffe auf unterschiedliche Speicherbänke

beziehen, wie z.B. mit unmittelbar aufeinander folgenden Adressen.

Die Verwendung eines verschränkten Speichers ist prinzipiell in jedem Rechner,

also unabhängig von der Prozessorarchitektur, möglich. In Vektorrechnern wirkt

sich jedoch positiv aus, dass die einzelnen Elemente meist in benachbarten Zellen

Search WWH ::

Custom Search