Information Technology Reference

In-Depth Information

2-Adressbefehle verarbeitet werden, und zwar deshalb, weil das Lesen der Operan-

den und das Schreiben eines Ergebnisses normalerweise in unterschiedlichen Fließ-

bandstufen geschieht und daher entkoppelt sein muss. Während nämlich das Ergeb-

nis eines Befehls in den Registerspeicher geschrieben wird, ist es nämlich ggf. not-

wendig zeitgleich die Operanden eines anderen nachfolgenden Befehls zu lesen.

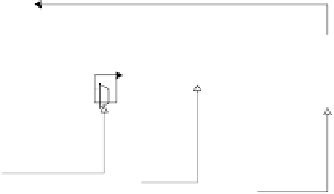

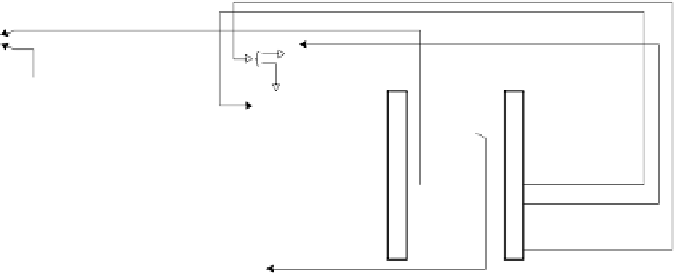

Falls man die Registertransferschaltung in Bild 2.19 noch um einen Datenspeicher

erweitert, kann sogar ein zusätzlicher, vierter Port notwendig sein. Dies ist davon

abhängig, ob auf den Datenspeicher innerhalb der Execute-Stufe, einer zusätzlichen

Stufe oder der Write-Back-Stufe zugegriffen wird. In den ersten beiden Fällen muss

nämlich bei Speicherebefehlen zeitgleich auf die zur Adressberechnung notwendi-

gen zwei und den im Datenspeicher abzulegenden dritten Operanden zugegriffen

werden, so dass ein vierter Port erforderlich ist, um das Ergebnis des versetzt in

Bearbeitung befindlichen Befehls innerhalb der Write-Back-Stufe in den Register-

speicher schreiben zu können. Ein Prozessor mit vierstufigem Fließband, der Daten-

zugriffe innerhalb der Write-Back-Stufe verarbeitet und deshalb statt vier nur drei

Registerports benötigt, ist in Bild 2.20 gezeigt. Er ist von der in Bild 2.7 dargestell-

ten Registertransferstruktur abgeleitet und besitzt viele Funktionalitäten realer Pro-

zessoren, wie z.B. die Möglichkeit, Operanden unmittelbar zu adressieren, Sprünge

befehlszählerrelativ auszuführen oder Unterprogramme zu verarbeiten.

1. Stufe

(Fetch)

2. Stufe

(Decode)

3. Stufe

(Execute)

4. Stufe

(Write Back)

+

+1

Befehls-

speicher

Register-

speicher

Daten-

speicher

ALU

0

Befehlsdecoder

Bild 2.20.

Prozessor mit vierstufigem Fließband, der aus der in Bild 2.7 dargestellten Registertrans-

ferschaltung abgeleitet wurde und der in seiner Funktionalität die wesentlichen Merkmale realer

Prozessoren besitzt

Es ist nicht sinnvoll, die Anzahl der Stufen eines Fließbands zu vergrößern, ohne

gleichzeitig eine Verkürzung des kritischen Pfads zu erreichen. Sollte z.B. die Takt-

frequenz des zweistufig arbeitenden Prozessors in Bild 2.18 durch die Fetch-Stufe

begrenzt sein, was wegen der geringen Zugriffsgeschwindigkeit auf große Speicher

wahrscheinlich ist, wird durch Unterteilung der Execute-Stufe in drei weitere Fließ-

bandstufen (entsprechend Bild 2.19) die Registertransferschaltung zwar komplizier-

ter, aber nicht höher taktbar. In beiden Fällen ist die Fetch-Stufe nämlich unverän-

dert langsam.

Search WWH ::

Custom Search