Information Technology Reference

In-Depth Information

Diese Art der überlappenden Befehlsausführung wird als

Fließbandverarbeitung

(

pipelining

), das Instruktionsregister auch als

Fließbandregister

(

pipeline register

)

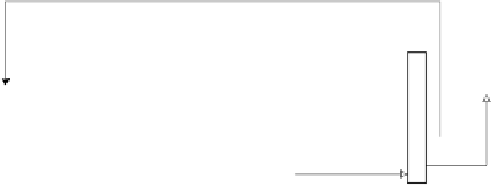

bezeichnet. Ein in Fließbandtechnik arbeitender Prozessor entsprechend Bild 2.18

bearbeitet zwei Befehle in zwei Takten, im Durchschnitt also einen Befehl pro Takt,

wobei man durch Verkürzung des kritischen Pfads eine im Vergleich zu einem ohne

Fließbandtechnik arbeitenden Prozessor höhere Taktfrequenz erzielt.

Der hier dargestellte Prozessor besitzt zwei

Fließbandstufen

. Natürlich kann durch

Einfügen weiterer Fließbandregister der kritische Pfad sukzessive verkürzt und auf

diese Weise eine Vervielfachung der Taktfrequenz erreicht werden. In Bild 2.19 ist

dies für einen Prozessor mit vierstufigem Fließband dargestellt (ähnlich dem

CY7C601 von Cypress, einem nicht mehr gefertigten Prozessor mit skalarer

SPARC-Architektur [133]), wobei die Fließbandstufen durch das Instruktionsregis-

ter IR sowie die Fließbandregister ER (execute register) und WBR (write back

register) voneinander entkoppelt sind. Ein

Verknüpfungsbefehl

durchläuft in vier

Takten die Fließbandstufen

Fetch

(der Befehl wird aus dem Befehlsspeicher gele-

sen),

Decode

(der Befehl wird decodiert und die Operanden aus dem Registerspei-

cher geladen),

Execute

(die Operanden werden miteinander verknüpft) und

Write

Back

(das Ergebnis wird in den Registerspeicher geschrieben). Ein

Sprungbefehl

durchläuft in drei Takten die Fließbandstufen Fetch, Decode und Execute.

1. Stufe

(Fetch)

2. Stufe

(Decode)

3. Stufe

(Execute)

4. Stufe

(Write Back)

a

+1

c

Befehls-

speicher

Register-

speicher

ALU

M

1

b

e

Befehlsdecoder

d

Bild 2.19.

Einfacher Prozessor mit vierstufigem Fließband

In jedem Fall ist hierbei sicherzustellen, dass die in einer Fließbandstufe benötigten

Informationen jeweils zeitgleich ihren Bestimmungsort erreichen. So ist z.B. die im

Befehl codierte Zieladresse und das vom Befehlsdecoder erzeugte Schreibsignal

nicht direkt mit dem Registerspeicher verbunden, sondern über die Fließbandregis-

ter ER und WBR (mit a und b markierte Verbindungen). Aus einem ähnlichen

Grund wird die Zieladresse von Sprungbefehlen nicht am Ausgang des Instruktions-

registers IR, sondern am Ausgang des Fließbandregisters ER abgegriffen (c). Sie

muss nämlich im selben Takt den Multiplexer M

1

erreichen, wie das in der Execute-

Stufe erzeugte und über den Befehlsdecoder geführte Bedingungsergebnis (d und e).

Ein nach dem Fließbandprinzip arbeitender realer Prozessor wird normalerweise

eine kompliziertere Registertransferschaltung besitzen, als in Bild 2.19 dargestellt,

in ihrem Aufbau jedoch dieser Grundstruktur entsprechen. Zum Beispiel ist der

Registerspeicher auch dann als

3-Port-Speicher

zu realisieren, wenn ausschließlich

Search WWH ::

Custom Search