Information Technology Reference

In-Depth Information

bzw. Eingang eines Registers oder Speichers. In Bild 2.17 ist ein Kandidat für den

kritischen Pfad stark ausgezogen dargestellt (Befehlszähler, Befehlsspeicher, Regis-

terspeicher, ALU, Registerspeicher). Ob der Pfad tatsächlich kritisch ist, kann ohne

eine zeitgenaue Simulation der Registertransferschaltung hier nicht eindeutig fest-

gestellt werden.

2.2.2 Überlappende Befehlsverarbeitung

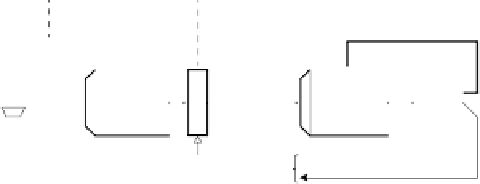

Eine einfache Technik zur Verkürzung des kritischen Pfads besteht darin, ihn mit

Hilfe eines Registers in zwei Teilpfade zu zerlegen, die im Idealfall jeweils doppelt

so schnell durchlaufen werden, wie der ursprüngliche, kritische Pfad. Die Register-

transferschaltung in Bild 2.17 lässt sich z.B. wie in Bild 2.18 dargestellt modifizie-

ren. Das Instruktionsregister IR (instruction register) teilt den ursprünglichen kriti-

schen Pfad vom Befehlszähler über Befehlsspeicher, Registerspeicher, ALU bis in

den Registerspeicher (siehe Bild 2.17) in die beiden Teilpfade Befehlszähler,

Befehlsspeicher, Instruktionsregister (a) und Instruktionsregister, Registerspeicher,

ALU, Registerspeicher (b).

1. Stufe (Fetch)

2. Stufe (Execute)

b

+1

Befehls-

speicher

Register-

speicher

ALU

M

1

a

c

Befehlsdecoder

Bild 2.18.

Einfacher Prozessor mit zweistufigem Fließband

Falls einer der beiden Teilpfade kritisch ist (was nicht der Fall sein muss - siehe z.B.

den mit c markierten Pfad) und die beiden Teilpfade eine ähnliche Laufzeit aufwei-

sen, ist die Taktfrequenz, mit der sich die Registertransferschaltung betreiben lässt,

so beinahe verdoppelt worden. Eine exakte Verdopplung wird jedoch nicht erreicht,

weil nämlich die Teilpfade in der Realität keine identischen Laufzeiten aufweisen

und das hinzugefügte Instruktionsregister eine Laufzeit besitzt, die man in den

neuen Teilpfaden berücksichtigen muss.

Zwar kann die Taktfrequenz durch das Einfügen des Instruktionsregisters nahezu

verdoppelt werden, jedoch benötigt ein einzelner Befehl zu seiner Verarbeitung nun

zwei statt eines Takts. Effektiv erreicht man durch das Instruktionsregister also eine

verlangsamte Befehlsverarbeitung. Allerdings besteht die Möglichkeit, Befehle

überlappend zu bearbeiten. Während der im Instruktionsregister gehaltene erste

Befehl zur Ausführung kommt (execute), d.h. die Operanden gelesen und verknüpft

werden, lässt sich zeitgleich bereits der unmittelbar folgende Befehl aus dem

Befehlsspeicher holen (fetch). Er wird im nächsten Taktschritt ausgeführt, wobei

sich parallel bereits ein weiterer Befehl aus dem Befehlsspeicher lesen lässt, usw.

Search WWH ::

Custom Search