Information Technology Reference

In-Depth Information

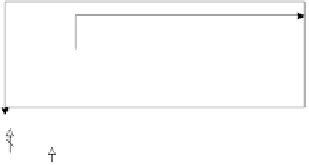

und die dort zum jeweiligen Ereignis gespeicherte Startadresse in ein Hilfsregister

geladen werden. Anschließend wird dessen Inhalt statt der Konstanten

IRQ-ADDR

über den Multiplexer M

5

in den Befehlszähler geladen.

c

Datenspeicher

+

b

+1

Befehls-

speicher

Datenwerk

M

5

Unterbrechungseingang

(irq)

Befehlsdecoder

CC

a

d

S

Bild 2.16.

Erweiterungen des Leitwerks zur Verarbeitung von Ereignissen

Damit verschachtelte Unterbrechungen möglich sind, wird von den meisten Prozes-

soren neben dem Inhalt des Befehlszählers zumindest der des Supervisor-Bits auto-

matisch gesichert. Der UltraSPARC IIIi von Sun benutzt hierzu z.B. ein einzelnes

als

Previous-Supervisor-Flag

bezeichnetes Bit im Statusregister [173]. Einige

CISC-Prozessoren

, z.B. der Pentium 4 von Intel, sichern mit Aufruf des Ausnahme-

programms automatisch den Inhalt des gesamten Bedingungsregisters [81]. Dies ist

sinnvoll, weil von zahlreichen Befehlen als Seiteneffekt die Bedingungsbits modifi-

ziert werden (bei einer Unterbrechung darf sich für das unterbrochene Programm

nichts verändern, um es später fehlerfrei fortsetzen zu können). Schließlich werden

von einigen Prozessoren, z.B. dem UltraSPARC IIIi von Sun oder dem

ARM7TDMI von ARM ltd., bei einer Ausnahmebehandlung sogar die Arbeitsregis-

ter automatisch gesichert. In beiden Fällen werden dabei die zu sichernden Register

ausgeblendet und in ihrer Funktion durch separat realisierte Register ersetzt (siehe

Abschnitt 1.4.2).

2.2 Fließbandverarbeitung (pipelining)

Mit den im vorangehenden Abschnitt beschriebenen Prinzipien können Prozessoren

mit sehr komplexen Programmiermodellen, wie z.B. dem des Pentium 4 oder des

PowerPC 970 implementiert werden. Derart realisierte Prozessoren stellen aufgrund

der geringen Arbeitsgeschwindigkeit jedoch keine ernstzunehmenden Konkurrenten

für die Originale von Intel bzw. IBM dar. In modernen Prozessoren sind nämlich zu

einem großen Teil Prinzipien realisiert, die einzig der Durchsatzerhöhung, mit

denen die Befehle verarbeitet werden, dienen.

Viele dieser Prinzipien sind aus Programmierersicht transparent, d.h. werden bei der

Programmierung nicht durch eine veränderte Semantik, sondern lediglich durch ein

verändertes Zeitverhalten bei Ausführung der Befehle bemerkt. Dies gilt auch für

die Fließbandverarbeitung, bei der eine Durchsatzerhöhung der Befehlsausführung

dadurch erreicht wird, dass man die

Taktfrequenz

, mit der ein Prozessor in der Lage

Search WWH ::

Custom Search