Information Technology Reference

In-Depth Information

{

Robustness in overload situations.

Basically, these properties had already been investigated by the GSPN sim-

ulations. However, the criticality of the FTC throughput properties required to

re-validate these aspects with dynamic testing, since simulation models are gen-

erally based on some simplifying assumptions about the behaviour of hardware

components, schedulers and processes.

A specic problem had to be solved in the test conguration development:

The FTC has been designed as a fault-tolerant multi-purpose system, where

dierent application layers may be installed on top of the ASS layer. As a con-

sequence, no specic application software was available, and a

test application

software layer (TASL)

had to be developed such that successful execution of tests

using the TASL implies that the FTC will also run properly with any concrete

application layer.

4.2

The RT-Tester Tool

For FTC tests, the

tool developed by JP Software-Consulting (now

Veried Systems International GmbH) in cooperation with the TZI-BISS at Bre-

men University was used.

RT-Tester

has been designed to perform automated

hardware-in-the-loop tests for embedded real-time systems or software tests on

process and thread level. The

RT-Tester

RT-Tester

functional components are shown in

Figure 3.

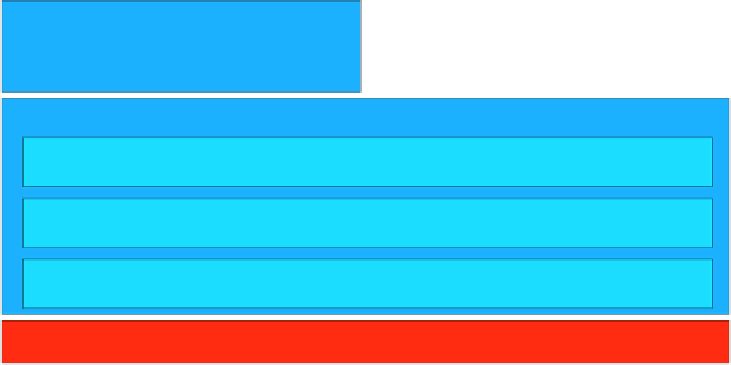

TEST MANAGEMENT FRONT-ENDS

www-based interface for integrated (remote) access of RT-Tester components

TEST SPECIFICATION SUB-SYSTEM

develop and validate test specifications

in various formalisms

TEST VISUALIZATION SUB-SYSTEM

on-line visualization of test executions

in various presentation techniques

REAL-TIME TEST SUB-SYSTEM

ABSTRACT MACHINE LAYER

Test generation - real-time test execution - on-the-fly test evaluation

COMMUNICATION CONTROL LAYER

Refinement - abstraction - relaying of test data

INTERFACE MODULE LAYER

implements direct interfaces to the System under Test

SYSTEM UNDER TEST

Fig. 3.

RT-Tester functional components.

Search WWH ::

Custom Search