Global Positioning System Reference

In-Depth Information

digital receiver ASIC(s) or FPGA(s), but even these devices can multiplex their digital

processes sequentially in order to reduce gate count if they are capable of running

faster than real time. Therefore, the ASIC, FPGA, and microprocessor programs can

be designed to be reentrant with a unique variable area for each receiver channel so

that only one copy of each algorithm is required to service all receiver channels. This

reduces the gate count or program memory requirements and ensures that every

receiver baseband processing function is identical. Digital multiplexing also elimi-

nates interchannel bias in the ASIC or FPGA (hardware portion of the digital

receiver) with no performance loss. (Section 7.2.7.2 further discusses interchannel

biases.)

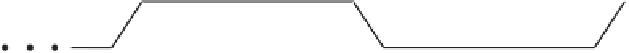

The three complex pairs of baseband

I

and

Q

signals from the digital receiver

may be resampled again by the integrate and dump accumulators. The total com-

bined duration of the receiver and processor integrate and dump functions estab-

lishes the predetection integration time for the signal. Normally, this cannot exceed

20 ms, which is the 50-Hz navigation message data bit period for the GPS C/A and

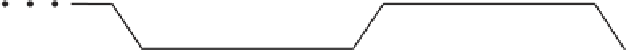

P(Y) code signals. Figure 5.4 illustrates the phase alignment needed to prevent the

predetection integrate and dump intervals from integrating across a SV data transi-

tion boundary. The start and stop boundaries for these integrate and dump func-

tions should not straddle the data bit transition boundaries because each time the SV

data bits change signs, the signs of the subsequent integrated

I

and

Q

data may

SV data transition

boundaries

20 ms

Receiver 20 ms

clock epochs

Bit sync phase skew (Ts)

FTF(n)

FTF(n+ 1)

FTF(n+ 2)

Misaligned integrate and dump phase

Predetection integration time

Aligned integrate and dump phase

Integrate

Dump

Figure 5.4

Phase alignment of predetection integrate and dump intervals with SV data transition

boundaries.

Search WWH ::

Custom Search