Global Positioning System Reference

In-Depth Information

input rate, which can be at 1,000 Hz during search modes or as low as 50 Hz during

track modes, depending on the desired dwell time during search or the desired

predetection integration time during track. The 50- to 1,000-Hz rates are well

within the servicing capability of modern high-speed microprocessors, but the 5- or

50-MHz rates are challenging even for modern DSPs. This further explains why the

high-speed but simple processes are implemented in a custom digital ASIC or FPGA,

while the low-speed but complex processes are implemented in a microprocessor.

The hardware integrate and dump process in combination with the baseband

signal processing integrate and dump process (described next) defines the

predetection integration time. Later, it will be shown that the predetection integra-

tion time is a compromise design. It must be as long as possible to operate under

weak or RF interference signal conditions, and it must be as short as possible to

operate under high dynamic stress signal conditions.

5.2.2 Baseband Signal Processing

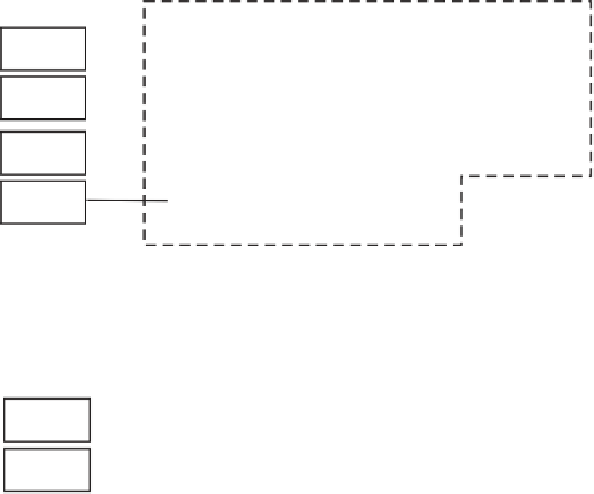

Figure 5.3 illustrates typical baseband code and carrier tracking loops for one

receiver channel in the closed loop mode of operation. The functions are typically

performed by the receiver processor shown in Figure 5.2. The combination of these

carrier and code tracking baseband signal processing functions and the digital

receiver channel carrier and code wipeoff and predetection integration functions

form the carrier and code tracking loops of one GPS receiver channel.

The baseband functions are usually implemented in firmware. Note that the

firmware need only be written once, since the microprocessor runs all programs

sequentially. This is contrasted to the usual parallel processing that takes place in the

Code loop discriminator

Integrate

and dump

Integrate

and dump

Integrate

and dump

Integrate

and dump

I

ES

I

E

Envelope

detector

Integrate

and dump

Q

ES

E

S

Q

E

Error

detector

Code loop

filter

I

LS

I

L

L

S

Integrate

and dump

Envelope

detector

Q

LS

Q

L

To code

NCO

Carrier

aiding

Code NCO

bias

Scale

factor

I

PS

Integrate

and dump

Integrate

and dump

I

P

Carrier loop

discriminator

Carrier loop

filter

To carrier

NCO

.

Q

PS

Q

P

Carrier NCO

bias

External

velocity aiding

Figure 5.3

Generic baseband processor code and carrier tracking loops block diagram.

Search WWH ::

Custom Search