Global Positioning System Reference

In-Depth Information

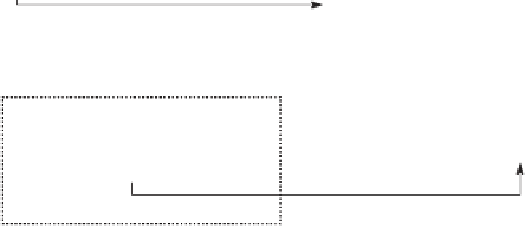

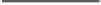

G1(t)

G1 register

1.023-MHz clock

1234 5 678 9 0

X1 epoch

Set to

"all ones"

X1 epoch

50-Hz

da

ta clock

R

C

÷

20

G2 register

12 3 4 5 6 78 9 10

1.023 MHz clock

.

.

.

.

R

÷

10

.

C

.

1023 decode

.

G epoch

1 KHz

.

X1 epoch

.

.

10.23-MHz

clock

C/A code

Gi(t)

G2(t + di Tg)

Phase select logic

Figure 4.10

C/A code generator.

the X1A register output is combined by an exclusive-or circuit with the X1B register

output to form the X1 code generator and that the X2A register output is combined

by an exclusive-or circuit with the X2B register output to form the X2 code genera-

tor. The composite X2 result is fed to a shift register delay of the SV PRN number in

chips and then combined by an exclusive-or circuit with the X1 composite result to

generate the P code.

The design specification for the P code calls for each of the four shift registers to

have a set of feedback taps that are combined by an exclusive-or circuit with each

other and fed back to their respective input stages. The polynomials that describe the

architecture of these feedback shift registers are shown in Table 4.4, and the logic

diagram is shown in detail in Figure 4.11.

Referring to Figure 4.11, note that the natural cycles of all four feedback shift

registers are truncated. For example, X1A and X2A are both reset after 4,092 chips,

eliminating the last three chips of their natural 4,095 chip sequences. The registers

X1B and X2B are both reset after 4,093 chips, eliminating the last two chips of their

natural 4,095 chip sequences. This results in the phase of the X1B sequence lagging

by one chip with respect to the X1A sequence for each X1A register cycle. As a

result, there is a relative phase precession between the X1A and X1B registers. A

similar phase precession takes place between X2A and X2B. At the beginning of the

GPS week, all of the shift registers are set to their initial states simultaneously, as

shown in Table 4.4. Also, at the end of each X1A epoch, the X1A shift register is

reset to its initial state. At the end of each X1B epoch, the X1B shift register is reset

to its initial state. At the end of each X2A epoch, the X2A shift register is reset to its

initial state. At the end of each X2B epoch, the X2B shift register is reset to its initial

state. The outputs (stage 12) of the A and B registers are combined by an exclu-

Search WWH ::

Custom Search