Information Technology Reference

In-Depth Information

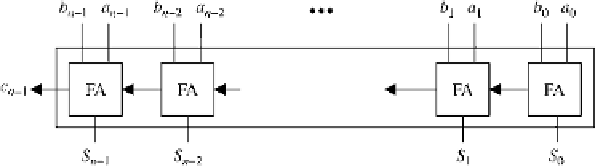

Figure 4.2

n-Bit carry-ripple through (CRT) adder

the series of carry outputs from the different stages as follows.

c

0

¼

G

0

þ

P

0

c

1

c

1

¼

G

1

þ

P

1

c

0

¼

G

1

þ

P

1

(G

0

þ

P

0

c

1

)

¼

G

1

þ

G

0

P

1

þ

P

0

P

1

c

1

c

2

¼

G

2

þ

P

2

c

1

¼

G

2

þ

P

2

(G

1

þ

G

0

P

1

þ

P

0

P

1

c

1

)

¼

G

2

þ

G

0

P

1

P

2

þ

G

1

P

2

þ

P

0

P

1

P

2

c

1

c

3

¼

G

3

þ

P

3

c

2

¼

G

3

þ

P

3

(G

2

þ

G

1

P

2

þ

G

0

P

1

P

2

þ

P

0

P

1

P

2

c

1

)

¼

G

3

þ

G

2

P

3

þ

G

1

P

2

P

3

þ

G

0

P

1

P

2

P

3

þ

P

0

P

1

P

2

P

3

c

1

.

The sequence of carry outputs shows total independence among the different car-

ries (broken carry chain). Figure 4.5 shows the overall architecture of a 4-bit CLA

adder. There are basically three blocks in a CLA. The first one is used to generate the

G

i

s and the P

i

s, while the second is used to create all the carry output. The third

block is used to generate all the sum outputs. Regardless of the number of bits in

the CLA, the delay through the first block is equivalent to a one gate delay, the

delay through the second block is equivalent to a two gate delay and the delay

through the third block is equivalent to a one gate delay. In Figure 4.5, we show

the generation of some carry and sum outputs. The reader is encouraged to complete

the design (see the Chapter Exercises).

B

A

Control

=

0/1

Add/Sub

C

Figure 4.3 Addition

/

subtraction logic network

Search WWH ::

Custom Search