Information Technology Reference

In-Depth Information

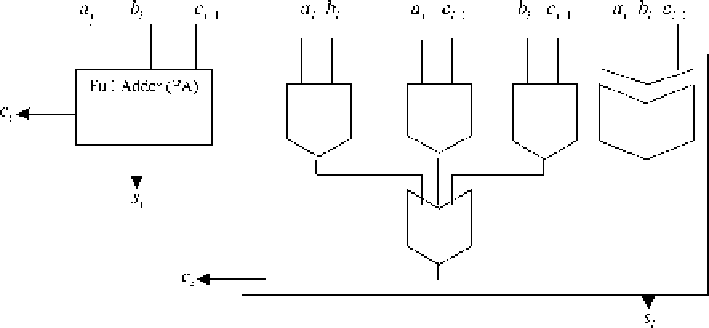

The output logic functions are given by s

i

¼

a

i

b

i

c

i

1

and c

i

¼

a

i

b

i

þ

a

i

c

i

1

þ

b

i

c

i

1

. The circuit used to implement these two functions is called a

full-adder (FA) and is shown in Figure 4.1.

Addition of two n-bit numbers A and B can be carried out using n consecutive

FAs in an arrangement known as a carry-ripple through adder (CRT), see Figure 4.2.

The n-bit CRT adder shown in Figure 4.2 can be used to add 2's complement

numbers A and B in which the b

n

1

and a

n

1

represent the sign bits. The same cir-

cuit can be used to perform subtraction using the relation B

A

¼

B

þ

A

þ

1.

Figure 4.3 shows the structure of a binary addition

subtraction logic network.

In this figure, the two inputs A and B represent the arguments to be added

/

sub-

tracted. The control input determines whether an add or a subtract operation is to be

performed such that if the control input is 0 then an add operation is performed while

if the control input is 1 then a subtract operation is performed. A simple circuit that

can implement the Add

/

/

Sub block in Figure 4.3 is shown in Figure 4.4 for the case

of 4-bit inputs.

One of the main drawbacks of the CRT circuit is the expected long delay between

the time the inputs are presented to the circuit until the final output is obtained. This

is because of the dependence of each stage on the carry output produced by the pre-

vious stage. This chain of dependence makes the CRT adder's delay O(n), where n is

the number of stages in the adder. In order to speed up the addition process, it is

necessary to introduce addition circuits in which the chain of dependence among

the adder stages must be broken. A number of fast addition circuits exist in the lit-

erature. Among these the carry-look-ahead (CLA) adder is well known. The CLA

adder is introduced below.

Consider the CRT adder circuit. The two logic functions realized are s

i

¼

a

i

b

i

c

i

1

and c

i

¼

a

i

b

i

þ

a

i

c

i

1

þ

b

i

c

i

1

. These two functions can be rewritten

in terms of two new subfunctions, the carry generate, G

i

¼

a

i

b

i

and the carry pro-

pagate, P

i

¼

a

i

b

i

. Using these two new subfunctions, we can rewrite the logic

equation for the carry output of any stage as c

i

¼

G

i

þ

P

i

c

i

1

. Now, we can write

Figure 4.1 The full-adder (FA) circuit

Search WWH ::

Custom Search