Information Technology Reference

In-Depth Information

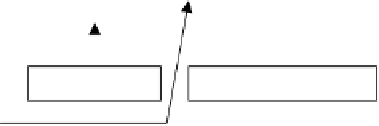

Shifted 16 bits

Displacement from

2

nd

word of instruction

Original 16 bits

7/15/31

0

15

0

Op Code

Address

Segment base

Address

å

å

BPR

Physical Address

Logical Address

Figure 3.9

Indirect addressing using BPR in the X86 family

Control transfer instructions in the X86 family include mainly four subtypes.

These are conditional, iteration, interrupt, and unconditional. A sample of these

instructions is shown in Table 3.12.

Processor control instructions in the X86 family include mainly three subtypes.

These are external synchronization, flag manipulation, and general control instruc-

tions. A sample of these instructions is shown in Table 3.13.

Having introduced the basic features of the instruction set of the X86 processor

family, we now move on to present a number of programming examples to show

TABLE 3.9 Sample of the X86 Data Movement Instructions

Mnemonic

Operation

Subtype

MOV

Move source to destination

General purpose

POP

Pop source from stack

General purpose

POPA

Pop all

General purpose

PUSH

Push source onto stack

General purpose

PUSHA

Push all

General purpose

XCHG

Exchange source with destination

General purpose

IN

Input to accumulator

Accumulator

OUT

Output from accumulator

Accumulator

XLAT

Table lookup to translate byte

Accumulator

LEA

Load effective address in register

Address-object

LMSW

Load machine status word

Address-object

SMSW

Store machine status word

Address-object

POPF

Pop flags off stack

Flag

PUSHF

Push flags onto stack

Flag

Search WWH ::

Custom Search