Information Technology Reference

In-Depth Information

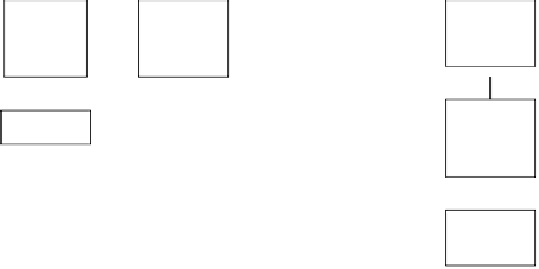

Local

History

Table

1024 × 10

Local

Prediction

Table

1024 × 3

Global

Prediction

4096

×

2

Choice

Prediction

4096 × 2

PC

MUX

Past

History

Branch

Prediction

Figure 10.11 The 21264 selection branch predictor

Global prediction is useful when the outcome of a branch can be inferred from the

direction of previous branches. Consider, for example, the case of repeated invoca-

tions of two branches. If the first branch that checks for a value equal to 1001 suc-

ceeds, the second branch that checks for the same value to be odd must also succeed.

The global history predictor can learn this pattern with repeated invocations of these

two branches.

The 2096

2 choice predictor is a table in which each entry holds a 2-bit saturat-

ing counter and is used to implement the selection (tournament) scheme. If the pre-

dictions of the local and global predictors differ, the 21264 updates the selected

choice prediction entry to support the correct predictor. The 21264 updates the

choice prediction table when a branch retires.

The slot assignment stage (S #2) simply assigns instructions to slots associated

with the integer and the floating-point queues.

The out-of-order (OOO) issue logic in the 21264 receives four fetched instruc-

tions every cycle, renames and remaps the registers (to avoid unnecessary register

dependencies), and queues the instructions until operands and

or functional units

become available. It dynamically issues up to six instructions every cycle, four inte-

ger and two floating-point instructions. Register renaming means mapping instruc-

tion virtual registers to internal physical registers. There are 31 integer and 31

floating-point registers that are visible to users. These registers are renamed

during execution to internal registers. It is only when instructions are finished

(retired) that the internal registers are renamed back to visible registers. Register

renaming eliminates write-after-write and write-after-read data dependencies. How-

ever, it preserves all the read-after-write dependencies that are necessary for correct

computation.

A list of the pending instructions is maintained by the OOO queue logic. In each

cycle, both the integer and the floating-point queues select those instructions that are

ready to execute. This selection is made based on a scoreboard of the renamed reg-

isters. The scoreboard maintains the status of renamed registers by tracking the

/

Search WWH ::

Custom Search