Information Technology Reference

In-Depth Information

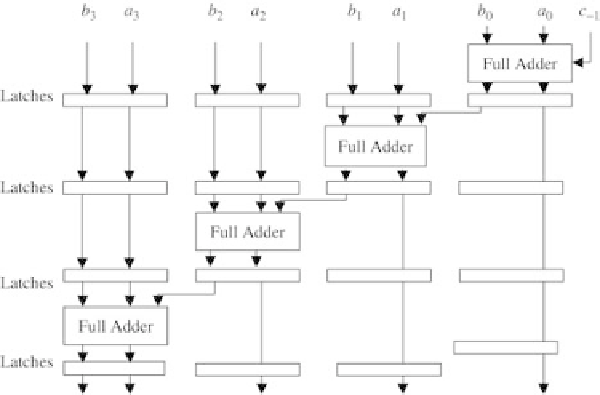

Figure 9.18 A modified 4-bit CRTA

It is possible to modify the CRTA in such a way that a number of pairs of

operands are operated upon, that is, pipelined, inside the adder, thus improving

the overall speed of addition in the CRTA. Figure 9.18 shows an example of a

modified 4-bit CRTA. In this case, the two operands A and B are presented to

the CRTA through the use of synchronizing elements, such as clocked latches.

These latches will guarantee that the movement of the partial carry values within

the CRTA are synchronized at the input of the subsequent stages of the adder

with the higher order operand bits. For example, the arrival of the first carry out

(c

0

) and the second pair of bits (a

1

and b

1

) is synchronized at the input of

the second full adder (counting from low order bits to high order bits) using

a latch.

Although the operation of the modified CRTA remains in principle the same; that

is, the carry ripples through the adder, the provision of latches allows for the possi-

bility of presenting multiple sets of pairs of operands to the adder at the same time.

Consider, for example, the case of adding M pairs of operands, whereby the oper-

ands of each pair are n-bit. The time needed to perform the addition of these M

pairs using a nonpipelined CRTA is given by T

np

¼

M

n

T

a

, where T

a

is the

time needed to perform single bit addition. This is to be compared to the time

needed to perform the same computation using a pipelined CTRA which is given

by T

pp

¼

(n

þ

M

2

1)

T

a

. For example, if M

¼

16 and

n

¼

64 bits, then we

have T

np

¼

T

a

, thus resulting in a speed-up of about

13. In the extreme case whereby it is possible to present unlimited number of

pairs of operands (M) to the CRTA at the same time, the speed up will reach 64,

the number of bits in each operand.

1024

T

a

and T

pp

¼

79

Search WWH ::

Custom Search