Information Technology Reference

In-Depth Information

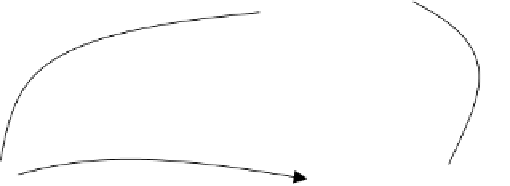

1. IRQ# Interrupt

Device

8259A

PIC

7. End Interrupt

3. INTA

6. Service

2. INTR

4. INT #

ISR

8. Return

CPU

5. Invoke

Figure 8.8

Interrupt handling in 80

86

increasing the number of interrupt inputs to 15. Figure 8.9 shows two PICS wired in

cascade. One PIC is designated as master and the other becomes the slave. As shown

in the figure, all slave interrupts are input via IRQ1 of the master. In general, eight

different slaves can be accommodated by a single PIC.

Example 2: ARM Interrupt Architecture

ARM stands for Advanced RISC

Machines. ARM is a 16

32-bit architecture that is used for portable devices because

of its low power consumption and reasonable performance. Interrupt requests to the

ARM core are collected and controlled by the interrupt controller, which is called

ATIC. The interrupt controller provides an interface to the core and can collect

up to 64 interrupt requests.

The usual sequence of events for interrupts is as follows. Interrupts would be

enabled at the source (such as a peripheral), then enabled in the interrupt controller,

and finally, enabled to the core. When an interrupt occurs at the source, its signal is

routed to the interrupt controller then to the ARM core. In the interrupt controller,

the interrupt can be enabled or disabled to the core and can be assigned a priority

/

TABLE 8.1 Standard IBM-PC Interrupt Type Numbers

for Typical Devices

IRQ

no.

Interrupt

type number

Device

Programmable interval timer

0

08H

Keyboard

1

09H

Cascading to the second PICs

2

Reserved

Serial communication port (COM2)

3

0BH

Serial communication port (COM1)

4

0CH

Fixed disk controller

5

0DH

Floppy disk controller

6

0EH

Parallel printer controller

7

0FH

Search WWH ::

Custom Search