Information Technology Reference

In-Depth Information

each belonging to a specific output device. In addition, a mechanism according to

which the processor can address those input and output registers must be adopted.

More than one arrangement exists to satisfy the abovementioned requirements.

Among these, two particular methods are explained below.

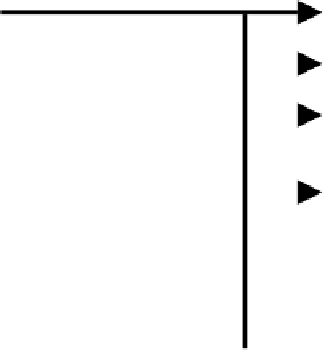

In the first arrangement, I

O devices are assigned particular addresses, isolated

from the address space assigned to the memory. The execution of an input instruc-

tion at an input device address will cause the character stored in the input register of

that device to be transferred to a specific register in the CPU. Similarly, the

execution of an output instruction at an output device address will cause the char-

acter stored in a specific register in the CPU to be transferred to the output register

of that output device. This arrangement, called shared I

/

O, is shown schematically

in Figure 8.2. In this case, the address and data lines from the CPU can be shared

between the memory and the I

/

O devices. A separate control line will have to be

used. This is because of the need for executing input and output instructions. In a

typical computer system, there exists more than one input and more than one

output device. Therefore, there is a need to have address decoder circuitry for

device identification. There is also a need for status registers for each input and

output device. The status of an input device, whether it is ready to send data to

the processor, should be stored in the status register of that device. Similarly, the

status of an output device, whether it is ready to receive data from the processor,

should be stored in the status register of that device. Input (output) registers,

status registers, and address decoder circuitry represent the main components of

an I

/

O interface (module).

/

Address Bus

Data Bus

Processor

Memory

Memory Control Lines

Input Device

(Keyboard)

Input Device(s) Control Lines

Output Device(s) Control Lines

Output Device

(Graphic Display)

Figure 8.2 Shared I

/

O arrangement

Search WWH ::

Custom Search