Information Technology Reference

In-Depth Information

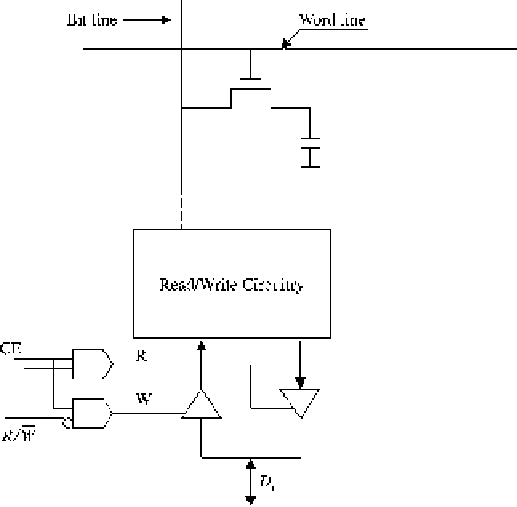

Figure 7.7 Dynamic memory array organization

As discussed before, appropriate internal organization of a memory subsystem

can lead to a saving in the number of IC pins required, an important IC design

factor. In order to reduce the number of pins required for a given dynamic

memory subsystem, it is a normal practice (as in the case of static memory) to

divide the address lines into row and column address lines. In addition, the row

and column address lines are transmitted over the same pins, one after the other

in a scheme known as time-multiplexing. This can potentially cut the number of

address pins required by half. Due to time-multiplexing of address lines,

it w

ill be

necessary to add two e

xtra

control lines, that is, row address strobe (RAS) and

column address strobe (CAS). These two control lines are used to indicate to the

memory chip when the row address lines are valid and when the column address

lines are valid, respectively. Consider, for example, the design of a 1M

1 dynamic

memory subsystem. Figure 7.8 shows a possible internal organization of the

memory cell array in which the array is organized as a 1024

1024.

It should be noted that only 10 address lines are shown. These are used to multi-

plex both the rows and columns address lines; each is 10 lines. The rows and col-

umns latches are used to store the row and column addresses for a dur

ation

equal

to the memory cycle. In th

is ca

se, a memory access will consist of a RAS and a

row address, followed by a CAS and a column address.

Search WWH ::

Custom Search