Information Technology Reference

In-Depth Information

Example 3

Compute the above three parameters for a memory system having the

following specification: size of the main memory is 4K blocks, size of the cache is

128 blocks, and the block size is 16 words. Assume that the system uses associative

mapping.

log

2

2

4

Word field

¼

log

2

B

¼

log

2

16

¼

¼

4 bits

log

2

2

7

2

10

Tag field

¼

log

2

M

¼

¼

12 bits

The number of bits

in the main memory address

log

2

(B

M)

log

2

¼

¼

(2

4

2

12

)

16 bits.

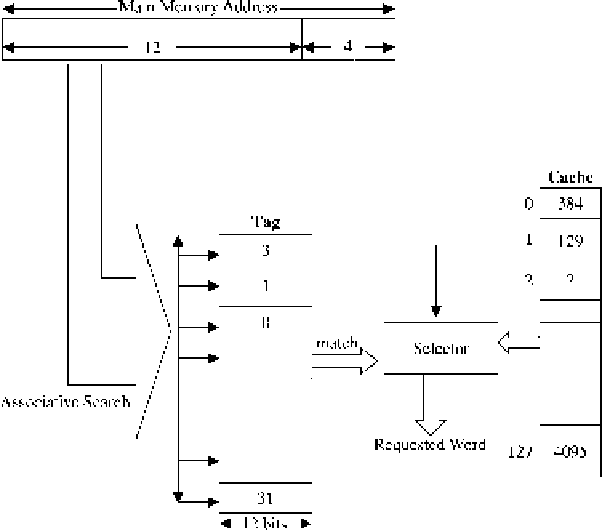

Having shown the division of the main memory address, we can now proceed to

explain the protocol used by the MMU to satisfy a request made by the processor for

accessing a given element. We illustrate the protocol using the parameters given in

the example presented above (see Fig. 6.8). The steps of the protocol are:

¼

1. Use the Tag field to search in the Tag memory for a match with any of the tags

stored.

2. A match in the tag memory indicates that the corresponding targeted cache

block determined in step 1 is currently holding the main memory element

requested by the processor, that is, a cache hit.

Figure 6.8 Associative-mapped address translation

Search WWH ::

Custom Search