Information Technology Reference

In-Depth Information

Tag

Cache

Main Memory

3

0

1

2

384

0

1

2

128

129

130

256

257

258

384

385

386

3968

1

0

129

126

127

31

127 255 383 4095

0 1 2 3 31

Figure 6.4 Mapping main memory blocks to cache blocks

4095

many-to-one mapping technique. The main advantage of the direct-mapping tech-

nique is its simplicity in determining where to place an incoming main memory

block in the cache. Its main disadvantage is the inefficient use of the cache. This

is because according to this technique, a number of main memory blocks may com-

pete for a given cache block even if there exist other empty cache blocks. This dis-

advantage should lead to achieving a low cache hit ratio.

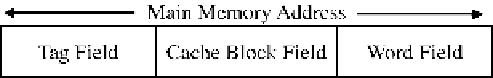

According to the direct-mapping technique the MMU interprets the address issued

by the processor by dividing the address into three fields as shown in Figure 6.5. The

lengths, in bits, of each of the fields in Figure 6.5 are:

1. Word field

¼

log

2

B, where B is the size of the block in words.

2. Block field

¼

log

2

N, where N is the size of the cache in blocks.

3. Tag field

log

2

(M

/

N), where M is the size of the main memory in blocks.

4. The number of bits in the main memory address

¼

log

2

(B

M)

¼

It should be noted that the total number of bits as computed by the first three

equations should add up to the length of the main memory address. This can be

used as a check for the correctness of your computation.

Example 2

Compute the above four parameters for Example 1.

log

2

2

4

Word field

log

2

B

¼

log

2

16

4 bits

¼

¼

¼

Block field

¼

log

2

N

¼

log

2

128

¼

log

2

2

7

¼

7 bits

log

2

(2

2

2

10

2

7

)

Tag field

log

2

(M

/

N)

5 bits

¼

¼

/

¼

The number of bits

in the main memory address

¼

log

2

(B

M)

¼

log

2

(2

4

2

12

)

¼

16 bits.

Figure 6.5 Direct-mapped address fields

Search WWH ::

Custom Search