Information Technology Reference

In-Depth Information

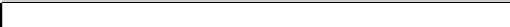

Tabl e 2.

HPWL comparison for IBM version 2 benchmarks

Circuits

Amoeba (A) Capo (C) Kapees (K)

×

10

6

×

10

6

×

10

6

K/A K/C

IBM01 easy

58.0278

55.8873

51.7759

0.89 0.92

IBM01 hard

57.6793

55.1354

51.456

0.89 0.93

IBM02 easy

165.906

158.743

146.253

0.88 0.92

IBM02 hard

164.541

156.048

145.224

0.88 0.93

IBM07 easy

373.388

368.7

354.121

0.94 0.96

IBM07 hard

359.586

355.686

353.964

0.98 0.99

IBM08 easy

406.834

387.502

352.928

0.86 0.91

IBM08 hard

395.116

379.512

363.081

0.91 0.95

IBM09 easy

341.532

317.126

311.554

0.91 0.98

IBM09 hard

338.188

321.029

321.057

0.94 1.00

IBM10 easy

605.746

636.689

601.824

0.99 0.94

IBM10 hard

642.065

629.543

624.721

0.97 0.99

IBM11 easy

521.413

481.637

478.191

0.91 0.99

IBM11 hard

514.758

476.332

472.878

0.91 0.99

Average

0.91 0.95

placers have reported their work on these benchmarks. For our experiments and

HPWL comparison we obtained the tool Cadence Encounter's Ameoba (version

9.1) and Capo (version 8.8) [12] from its respective websites.

The implementation of our tool, Kapees, for large scale standard cell place-

ment, is done in C language. The experiments are performed on 1.5 GHz, 32-bit,

2GB RAM, Intel dual core machine running Ubuntu, a variant of GNU-Linux, as

operating system. We compared our tool with Capo as they are run on the same

machine, whereas Amoeba run results are extracted on a different machine.

The run time of our tool is 10 times more when compared to that of Capo for

designs with cells less than 2000. For the design IBM01 easy, run time of Capo is

21 seconds, whereas, runtime of Kapees is 428 seconds, which means kapees is 22

times slower than Capo for this design. For the design IBM12 hard, run time of

Capo is 205 seconds, whereas, runtime of Kapees is 9084 seconds, which means

kapees is 44 times slower than Capo for this design. We observed that the runtime

of Kapees increases with the growth of number of cells. This is primarily due to

the use of simulated annealing technique wherein we perform HPWL calculation

for each iteratve move. We plan to improve run-time in future.

As reported in Table 2, the experiments show that the half perimeter wire

lengths obtained for these designs by Kapees are on an average 9% and 5%

less than that obtained from Amoeba and Capo, respectively. We get superior

results over other simulated annealing techniques because of our contribution as

the method2. Instead of using terminal propagation, we use method2 to improve

the already obtained cuts during global placement.