Information Technology Reference

In-Depth Information

Tabl e 3.

Multiple (two) fault diagnosis with 1-detect tests

Circuit No. of DC % of cases diagnosed CPU* Fault ratio

name Patterns % Both faults One fault No fault s SET1 SET2

C17 10 95.454 80.950 19.040 0.000 0.067 0.500 2.091

C432 462 94.038 90.566 7.547 1.886 0.135 0.563 3.516

C499 2080 98.000 49.056 20.754 30.188 0.613 0.371 17.589

C880 1664 94.161 86.792 9.433 3.773 0.502 0.900 3.205

C1908 3625 85.187 90.566 0.000 9.433 0.928 0.488 12.764

C2670 13300 85.437 88.679 3.773 7.547 4.720 0.564 7.046

C3540 3520 89.091 86.792 3.773 9.433 1.547 0.488 5.177

C5315 13899 91.192 98.113 1.886 0.000 7.065 0.422 3.886

C6288 1056 85.616 83.018 0.000 16.981 0.888 0.589 5.536

C7552 17064 86.507 96.226 1.886 1.886 7.539 0.358 7.104

∗

PC with Intel Core-2 duo 3.06GHz processor and 4GB memory

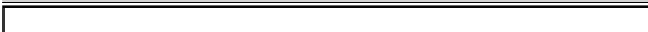

Fig. 5.

Fault masking (interference) in XOR gate

100% gives the percentage of cases where both faults were not diagnosed, as

shown in column 6. As the results in the table indicate, except for the circuit

C499, all other circuits have, at least in 80% cases, a perfect diagnosis of both

faults. A point to be noted is that the proposed diagnosis procedure does not

assume that fault masking is not present and the reported percentage of diagnosis

includes the possible fault masking and interference cases.

The reason for C499 (32-bit single-error-correcting circuit) producing poor

multiple fault diagnosis (resulting in irrelevant surrogate faults) even with a

test pattern set having very high diagnostic coverage (based on single stuck-at

faults) must be examined. We found the presence of circular fault masking in

many of the fault cases considered. The circuit has an XOR tree consisting of 104

two-input XOR gates. XOR logic gates are not considered to be elementary logic

gates since they are generally constructed from multiple Boolean gates, such that

the set of faults depends on its construction. All four test patterns are needed to

completely test a 2-input XOR gate, regardless of its construction [14]. Consider

the XOR gate shown in Figure 5. The top input has a stuck-at-1 (sa1) fault and

the bottom input has a stuck-at-0 (sa0) fault. To propagate a single fault through

XOR gate, the other input must be unchanged. But since this is a multiple fault

situation, two faults are trying to propagate through the XOR gate at the same

time. So a '0' on the top input is required to activate the sa1 fault and a '1' on

the bottom input is required to activate the sa0 fault. But since both inputs are

changed, the faults mask each other. This phenomenon is called circular masking.

Hence the output is '1' which is the same as the good circuit output. Due to

this circular masking, the algorithm will not be able to produce the relevant

surrogate faults as the actual faults are dropped, since the pattern which should

have failed, passes. This is not only for the case where both faults are present on