Information Technology Reference

In-Depth Information

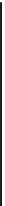

VDD

I

L

I

L

Pre

MP0

MP 1

WL1

I

Cell

1 M/M

I

CBL

I

CBL

0 M/M 1

X2

X1

C

BLB

C

BL

V

L

+ V

R

BL

M

P

3

MP2

V

L

X5

X6

MP2

MP4

M

P

5

CS

D

Ls

V

R

C

DLB

MP5

C

DL

MN1

M

N

2

SAEN

M

P

6

CS (gnd)

PREG

DL

MP9

MP7

M

P

8

MP10

X4

OutB

X3

Out

MN6

MN4

MN7

MN3

M

N

5

EQ

(a) (b) CMC analogy

Fig. 1.

Schematic of proposed SA

node X1 and X2 because the gate to source voltage of MP2 and MP4 will be same,

since their currents are equal, their sizes are equal and both devices are in saturation.

Same is the case for MP3 and MP5. Hence the voltage at node X1 is V

L

+V

R

[Fig. 2].

Similarly voltage at X2 will be the same. Transistors MP0 and MP1 are used to pull

the bit-lines close to the supply voltage to attain memory cell stability and soft error

immunity. CMC transfers the differential current to data-lines. Second sensing stage

consists of three PMOS (MP6-MP8) and seven NMOS (MN1-MN5) transistors. Here

MN1, MN2 are used to precharge the data-lines (DLs) to GND. The cross coupled

inverter amplifies the small voltage difference on the DLs to the full CMOS logic

level. MP9-MP10 and MN6-N7, forms two output inverters, serving as buffers to

drive the potentially large output loads to full CMOS logic output levels. Before any

read cycle MP0 and MP1 precharge the bit-line capacitances to V

DD.

Precharge tran-

sistors are upsized to charge large bit-line capacitances up to 3pF in order to account

for the effect of parasitic capacitances associated with large cells in the array. Simul-

taneously, MN1 and MN2 precharge the data-line capacitances to GND. Meanwhile,

Equal (EQ) signal turns on MN4 to equalize nodes X3 and X4 to the same potential.

MP6 is kept in cut-off mode by asserting SAEN logic “HIGH”, thereby saving static

power. Nodes X3 and X4 will also be at low potential (near V

th

) during standby as a

result, implying both the NMOS devices (MN6, MN7) operates in cutoff mode con-

suming no DC current by these buffers except subthreshold current. The second sens-

ing stage ensures that the standby current of the circuit and thus the power dissipation

is minimized because of sleeping MP6. Once Word Line (WL1) and Column Select