Information Technology Reference

In-Depth Information

2.4

Temperature

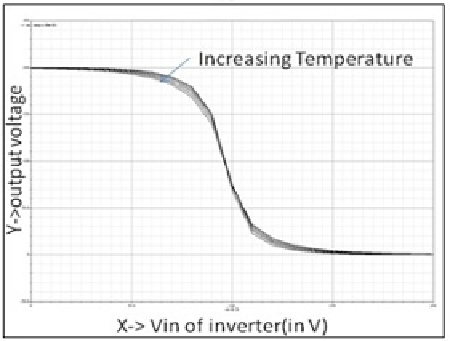

Another challenge for digital design in the subthreshold region is the effect of temper-

ature variations on circuit behavior. During strong inversion operation, a rise in tem-

perature generally slows down circuits due to mobility degradation. However, a rise

in temperature causes a fall in threshold voltage, V

T

which exponentially increases

subthreshold current. At a certain temperature, this increase overtakes the mobility

degradation and subthreshold circuits get faster. On the other side of the temperature

scale, cooling down a circuit not only increases mobility, but also minimizes subthre-

shold leakage. At very low temperatures, the drain leakage becomes so minimal that

the temperature insensitive gate leakage becomes the primary leakage. Further drops

in temperature don't change the leakage. The effect of temperature change from 0

0

C

to 100

0

C on the VTC of a minimum sized inverter in UMC 90nm process at a typical

corner is shown in Fig. 3.

Fig. 3.

VTC of an inverter at various operating temperatures

2.5

Impact of Scaling

It might appear that since the target frequencies for the subthreshold circuits are of the

order of MHz or lower, scaling is unnecessary. However, scaled subthreshold circuits

have the following advantages for conventional planar MOSFETs: (1) Smaller devic-

es have lower capacitance and hence, lower switching power. (2) Gate oxide thick-

ness (tox) is smaller, which increases the gate control.

3

32-Bit Kogge-Stone Adder Architecture

The concept of KS adder is used in order to reduce the delay of the digital circuits.

This adder has the complexity of O(log2n) [7]. It combines two carry words at a time

at each level of hierarchy. The total adder requires 129 complex logic gates each to

implement the dot operator. In addition, 32 logic modules are needed for the genera-

tion of the propagate and generate signals at the first level (pi and gi) as well as 16