Information Technology Reference

In-Depth Information

If cache miss then data is loaded from

DRAM memory into cache and to the

microprocessor (cache controller will

try and guess right next time)

DRAM

memory

Cache

controller

Microprocessor

Controller loads memory

from DRAM into cache memory

If cache hit then

microprocessor

loads for cache

memory

Cache

memory

(SRAM)

Figure A.8

Cache operation

Cache architecture

The main cache architectures are:

•

Look-through cache

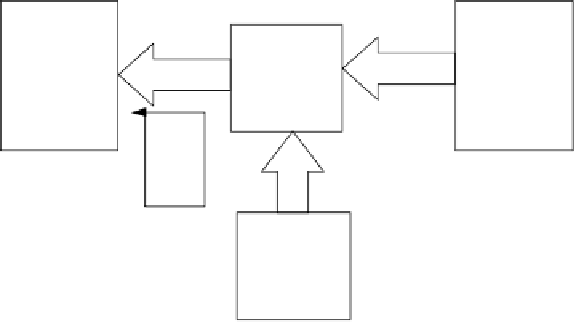

. In a look-through cache the system memory is isolated from the

processor address and control busses. In this case the processor directly sends a memory

request to the cache controller which then determines whether it should forward the re-

quest to its own memory or the system memory. Figure A.9 illustrates this type of cache.

It can be seen that the cache controls whether the processor address contents are latched

through to the DRAM memory and it also controls whether the contents of the DRAMs

memory is loaded onto the processor data bus (through the data transceiver). The opera-

tion is described as bus cycle forwarding.

•

Look-aside cache

. A look-aside cache is where the cache and system memory connect to

a common bus. System memory and the cache controller see the beginning of the proces-

sor bus cycle at the same time. If the cache controller detects a cache hit then it must in-

form the system memory before it tries to find the data. If a cache miss is found then the

memory access is allowed to continue.

•

Write-through cache

. With a write-through cache all memory address accesses are seen

by the system memory when the processor performs a bus cycle.

•

Write-back cache

. With a write-back cache all system writes are controlled by the cache

controller. It thus does not write the system memory unless it has to.