Information Technology Reference

In-Depth Information

The frequency of the crystal is twice the frequency of the received signal. It is so constant

that it only needs irregular and small adjustments to be synchronised to the received signal.

The function of the phase detector is to find irregularities between the two signals and adjust

the VCO to minimise the error. This is accomplished by comparing the received signals and

the output from the VCO. When the signals have the same frequency and phase the PLL is

locked. Figure 26.20 shows the PLL components and the function of the EXOR.

Phase

detector

Low-pass

filter

out

ref

control voltage

VCO

sig

ref

out

control voltage

Figure 26.20

PLL and example waveform for the phase detector

26.12.3 Memory buffer

The rate at which data is transmitted on the cable differs from the data rate used by the re-

ceiving computer, and the data appears in bursts. To compensate for the difference between

the data rate, a first-in first-out (FIFO) memory buffer is used to produce a constant data rate.

An important condition is that the average data input rate should not exceed the frequency of

the output clock; if this is not the case the buffer will be filled up regardless of its size.

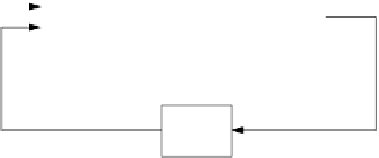

A FIFO is a RAM that uses a queuing technique where the output data appears in the

same order that it went in. The input and output are controlled by separate clocks, and the

FIFO keeps track of the data that has been written and the data that has been read and can

thus be overwritten. This is achieved with a pointer. Figure 26.21 shows a block diagram of

the FIFO configuration. The FIFO status is indicated by flags, the empty flag (EF) and the

full flag (FF), which show whether the FIFO is either empty or full.

26.12.4 Ethernet implementation

The completed circuit for the Ethernet receiver is given in Section 26.15 and is outlined in

Figure 26.22. It uses the SEEQ Technologies 82C93A Ethernet transceiver as the receiver

and the SEEQ 8020 Manchester code converter which decodes the Manchester code. A

transformer and a dc-to-dc converter isolate the SEEQ 82C92A and the network cable from

the rest of the circuit (and the computer). The isolated dc-to-dc converter converts a 5 V sup-

ply to the

-

9 V needed by the transceiver.

The memory buffer used is the AMD AM7204 FIFO which has 4096 data words with 9-

bit words (but on

ly

ei

gh

t

bits

a

re

actua

lly

used). The output of the circuit is eight data lines,

the control lines

FF

,

EF

,

RS

,

R

and

W

, and the +5 V and GND supply rails.