Information Technology Reference

In-Depth Information

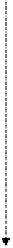

HostClk

PeriphAck

D0-D7

First byte

Second byte

HostAck

Data

Command

12

3

4

Figure 17.7

ECP forward data and command cycle

In the forward mode, the transfer of the data is from the host to the peripheral. Initially the

host places its data on the data bus. It sets the HostAck line high to indicate a data cycle and

sets HostClk low to indicate valid data. Next, the peripheral acknowledges the host by setting

PeriphAck high. The host sets HostClk high which clocks the data into the peripheral. After

this, the peripheral sets PeriphAck low to indicate that it is ready for the next byte.

Figure 17.7 illustrates an example of the reverse channel transfer where the peripheral

transfers information to the host. As before, it shows a command cycle followed by a data

cycle. It is similar to the forward phase except that the host requests a reverse channel by

setting the nReverseRequest low. The peripheral then sets the nAckReverse line low to indi-

cate that it is ready to transfer data, then it puts the data on the data bus. It then sets the Pe-

riphAck high to indicate that it is a data cycle and set PeriphClk low to indicate valid data.

After this the host sets HostAck high to acknowledge these events and the peripheral sets

PeriphClk high. This clock edge then clocks the data into the host. Finally, the host sets

HostAck low to indicate that it is ready for the next byte.

17.6.1 ECP software and register interface

The ECP specification ('The IEEE 1284 Extended Capabilities Port Protocol and ISA Inter-

face Standard') defines a number of operational modes. These are defined in Table 17.6. The

registers used to program ECP are based on the standard parallel port setting and uses an

address which are offset by 1024 (400h) from the standard port address. Thus:

Standard port base address = 378h

ECP extended registers

= 378h + 400h = 778h

There are six extra registers defined for ECP, these are given in Table 17.7. These six regis-

ters are mapped into three memory addresses and are shown in Figure 17.8 (778h, 779h and

77Ah). The ECR register used to set the current operational mode and can also be used to

determine if an ECP-capable port is installed in the PC. Detection software can try to access

any ECR registers by adding 402h to the base address of the LPT ports identified in the

BIOS LPT port table.