Information Technology Reference

In-Depth Information

2. The program reads from the status register to test to see if the BUSY signal is LOW (that

is, the printer is not busy)

3. If the printer is not busy t

hen the p

rogram sets the

STROBE

line active LOW.

4. Program then makes the

STROBE

line HIGH by de-asserting it.

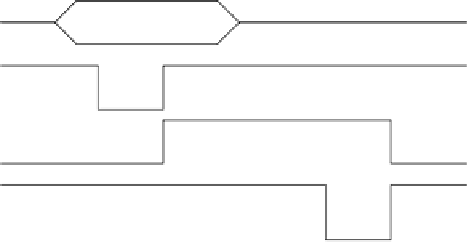

Valid data

DATA

STROBE

BUSY

ACK

0.5ms (min.)

5

m

s (min.)

Figure 17.1

Compatibility mode transfer

17.3 Nibble mode

This mode defines how four bits are transferred, at a time, using status lines for the input data

(sometimes known as Hewlett Packard Bi-tronics). The Nibble mode can thus be used for bi-

directional communication, with the data lines being used as outputs. To input a byte, re-

quires two nibble cycles.

As seen in

Chapte

r 16 there are five inputs from the parallel port (BUSY,

ACK

, PE,

SELECT and

ERROR

). The status of these lines can be found by simply reading the upper

five bits of the status register. The BUSY, PE, SELECT and

ERROR

are normally used as

ACK

used to interrupt the processor.

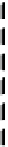

Table 17.1 defines the names of the signal in the nibble mode and Figure 17.2 shows the

handshaking for this mode.

The nibble mode has the following sequence:

1. Host (PC) indicates that it is ready to receive data by setting HostBusy LOW.

2. The peripheral then places the first nibble on the status lines.

3. The peripheral indicates that the data is valid on the status line by setting PtrClk low.

4. The host then reads from the status lines and sets HostBusy high to indicate that it has

received the nibble, but it is not yet ready for another nibble.

5. The peripheral sets PtrClk HIGH as an acknowledgement to the host.

6. Repeat steps 1-5 for the second nibble.