Information Technology Reference

In-Depth Information

Break

0 - Normal output

1 - Send a break

Stick bit

0 - No stick bit

1 - Stick bit

Stop bits

0 - 1 stop bit

1 - 1.5 stop bits

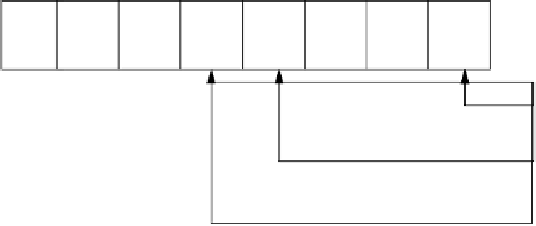

C

7

C

6

C

5

C

4

C

3

C

2

C

1

C

0

Set bits per word

00 - 5 bits, 01 - 6 bits

10 - 7 bits, 11 - 8 bits

Register address

discriminator

Parity bit

0 - No parity

1 - Parity

Parity type

0 - Even parity

1 - Odd parity

Figure 13.17

Line control register

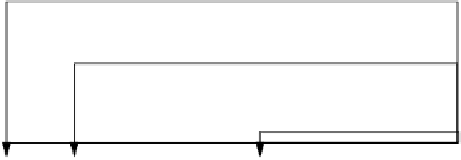

The MSB, C

7

, must to be set to a '0' in order to access the transmitter and receiver buff-

ers, else if it is set to a '1' the baud rate divider is set up. The baud rate is set by loading an

appropriate 16-bit divisor into the addresses of transmitter/receiver buffer address and the

next address. The value loaded depends on the crystal frequency connected to the IC. Table

13.4 shows divisors for a crystal frequency of 1.8432 MHz. In general, the divisor,

N

, is re-

lated to the baud rate by:

Clock

frequency

Baud

rate

=

16

×

N

10

6

/(9600

For example, for 1.8432 MHz and 9600 baud

N

= 1.8432

×

×

16) = 12 (000Ch).

Table 13.4

Baud rate divisors

Baud rate

Divisor (value loaded into Tx/Rx buffer)

110

300

600

1200

1800

2400

4800

9600

19200

0417h

0180h

00C0h

0060h

0040h

0030h

0018h

000Ch

0006h

Register addresses

The addresses of the main registers are given in Table 13.5. To load the baud rate divisor,

first the LCR bit 7 is set to a '1', then the LSB is loaded into divisor LSB and the MSB into