Information Technology Reference

In-Depth Information

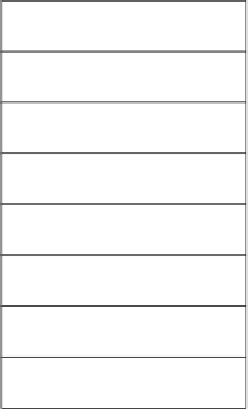

Base address

COM1: 3F8h

COM2: 2F8h

Base address

TD/RD

Interrupt enable

Base address+1

Interrupt Identity

Base address+2

Line control

Base address+3

Modem control

Base address+4

Line status

Base address+5

Modem status

Base address+6

Scratch pad

Base address+7

Figure 13.14

Serial communication registers

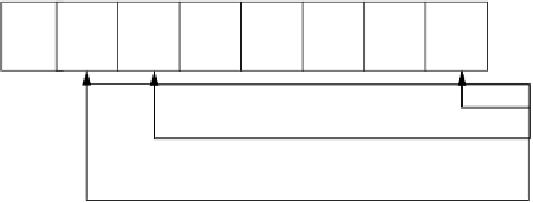

Line Status Register (LSR)

The LSR determines the status of the transmitter and receiver buffers. It can only be read

from, and all the bits are automatically set by hardware. The bit definitions are given in Fig-

ure 13.15. When an error occurs in the transmission of a character one (or several) of the

error bit is (are) set to a '1'.

Overrun error

Parity error

Framing error

Break detected

0

S

6

S

5

S

4

S

3

S

2

S

1

S

0

Set to 1 when data

has been received

Set to 1 when transmitter

buffer contents loaded

into transmit register

Set to 1 when transmitter

buffer is empty

Figure 13.15

Line status register

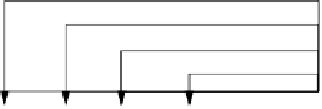

One danger when transmitting data is that a new character can be written to the transmitter

buffer before the previous character has been sent. This overwrites the contents of the

character being transmitted. To avoid this the status bit S

6

is tested to determine if there is

still a character in the buffer. If there is then it is set to a '1', else the transmitter buffer is