Information Technology Reference

In-Depth Information

8.3

PCMCIA registers

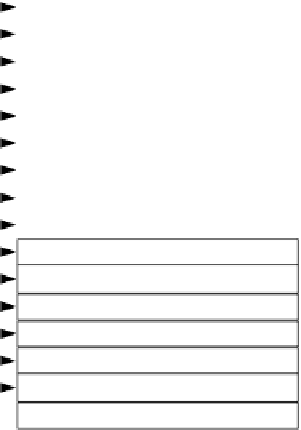

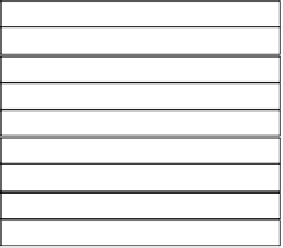

A typical PCMCIA interface controller (PCIC) is the 82365SL. Figure 8.1 shows the main

registers for the first socket. The second socket index values are simply offset by 40h. Figure

8.2 shows that the base address of the PCIC is, in Windows, set to 3E0h, by default. Figure

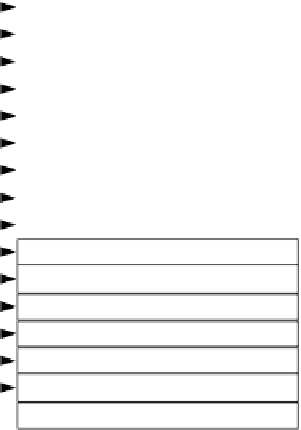

8.3 shows an example of a FIRST and LAST memory address. The PCIC is accessed using

two addresses: 3E0h and 3E1h. The I/O windows 0/1 are accessed through:

•

08h/0Ch for the low byte of the FIRST I/O address.

•

09h/0Dh for the high byte of the FIRST I/O address.

•

0Ah/0Eh for the high byte of the LAST I/O address.

•

0Bh/0Fh for the high byte of the LAST I/O address.

The registers are accessed by loading the register index into 3E0h and then the indexed regis-

ter is accessed through the 3E1h. The memory windows 0/1/2/3/4 are accessed through:

•

10h/18h/20h/28h/30h for the low byte of the FIRST memory address.

•

11h/19h/21h/29h/31h for the high byte of the FIRST memory address.

•

12h/1Ah/22h/2Ah/32h for the low byte of the LAST memory address.

•

13h/1Bh/23h/2Bh/33h for the high byte of the LAST memory address.

•

14h/1Ch/24h/2Ch/34h for the low byte of the card offset.

•

15h/1Dh/25h/2Dh/35h for the high byte of the card offset.

Register index

Register index

PCIC identification

Interface status

Power supply (RESETDRV)

Interrupt control

Card status change

Configuration

Memory window enable

I/O window control

FIRST setup for I/O window 0 (lo)

PCIC identification

Interface status

Power supply (RESETDRV)

Interrupt control

Card status change

Configuration

Memory window enable

I/O window control

FIRST setup for I/O window 0 (lo)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

FIRST setup for I/O window 0 (hi)

LAST setup for I/O window 0 (lo)

LAST setup for I/O window 0 (hi)

FIRST setup for I/O window 1 (lo)

FIRST setup for I/O window 1 (hi)

LAST setup for I/O window 1 (lo)

LAST setup for I/O window 1 (hi)

FIRST setup for I/O window 0 (hi)

LAST setup for I/O window 0 (lo)

LAST setup for I/O window 0 (hi)

FIRST setup for I/O window 1 (lo)

FIRST setup for I/O window 1 (hi)

LAST setup for I/O window 1 (lo)

LAST setup for I/O window 1 (hi)

0Dh

0Eh

0Fh

10h

0Dh

0Eh

0Fh

10h

FIRST setup for memory window 0 (lo)

FIRST setup for memory window 0 (hi)

LAST setup for memory window 1 (lo)

LAST setup for memory window 1 (hi)

FIRST setup for memory window 0 (lo)

FIRST setup for memory window 0 (hi)

LAST setup for memory window 1 (lo)

LAST setup for memory window 1 (hi)

11h

12h

13h

11h

12h

13h

Figure 8.1

PCMCIA controller status and control registers