Information Technology Reference

In-Depth Information

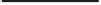

the data in burst mode when it has enough data. Figure 4.3 shows an example where the PCI

bridge buffers the incoming data and transfers it using burst mode. The transfers between the

processor and the PCI bridge, and between the PCI bridge and the PCI bus can be independ-

ent where the processor can be transferring to its local memory while the PCI bus is transfer-

ring data. This helps to decouple the PCI bus from the processor.

The primary bus in the PCI bridge connects to the processor bus and the secondary bus

connects to the PCI bus. The prefetch buffer stores incoming data from the connected bus

and the posting buffer holds the data ready to be sent to the connected bus.

The PCI bus also provides for a configuration memory address (along with direct mem-

ory access and isolated I/O memory access). This memory is used to access the configuration

register and 256-byte configuration memory of each PCI unit.

Processor

bus

PCI bus

Address1

Data1

Address2

Data2

Address3

Data3

Prefetch

buffer

Posting

buffer

Address1

Data1

Data2

Data3

Data4

Processor

Prefetch

buffer

Address4

Data4

Posting

buffer

PCI bridge

transfers with

burst mode

Primary

bus

Secondary

bus

Figure 4.3

PCI bridge using buffering for burst transfer

4.2.1 PCI bus cycles

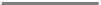

The PCI has built-in intelligence where the command/byte enable signals (

C/BE3

-

C/BE0

) are

used to identify the command. They are given by:

C/BE3

C/BE2

C/BE1

C/BE0

Description

INTA sequence

0

0

0

0

Special cycle

0

0

0

1

I/O read access

0

0

1

0

I/O write access

0

0

1

1

0

1

1

0

Memory read access

Memory write access

0

1

1

1

Configuration read access

1

0

1

0

Configuration write access

1

0

1

1

Memory multiple read access

1

1

0

0

Dual addressing cycle

1

1

0

1

Line memory read access

1

1

1

0

Memory write access with invalidations

1

1

1

1

The PCI bus allows any device to talk to any other device, thus one device can talk to an-