Information Technology Reference

In-Depth Information

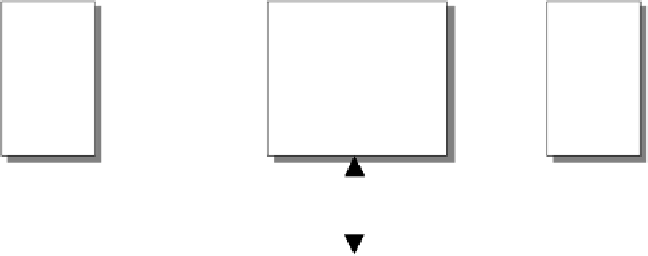

Intel have developed a standard interface, named the PCI (Peripheral Component Inter-

connection) local bus, for the Pentium processor. This technology allows fast memory, disk

and video access. A standard set of interface ICs known as the 82430 PCI chipset is available

to interface to the bus. Figure 4.1 shows how the PCI bus integrates into the PC. The proces-

sor runs at a multiple of the motherboard clock speed, and is closely coupled to a local

SRAM cache (first-level, or primary, cache). If the processor requires data it will first look in

the primary cache of its contents. If it is in this cache it will read its contents, and there is

thus no need to either read from the second level cache or from DRAM memory. If the data

is not in the primary cache then the processor slows downs to the motherboard clock speed,

and contacts the system controller (which contains a cache controller). The controller then

examines the second-level cache and if the contents are there, it passes the data onto the

processor. If it does not have the contents then DRAM memory is accessed (which is a rela-

tively slow transfer).

The system controller also interfaces to PCI bus, which is running at the motherboard

clock frequency. This then bridges onto other busses, such as ISA, IDE and USB, each of

which is running at different clock rates. The PCI bus thus provides a foundation bus for

most of the internal and external busses.

Local bus design involves direct access to fast address and data busses. The ISA bus was

a great bottleneck because it could only run at 8 MHz. This chapter discusses the VL-local

bus and the PCI bus. The PCI bus is now the main interface bus used in most PCs, and is rap-

idly replacing the ISA bus for internal interface devices. It is a very adaptable bus and most

of the external busses, such as SCSI and USB connect to the processor via the PCI bus.

SRAM cache

memory

SRAM cache

memory

SRAM tag address

DRAM

addresses

Address

bus

System

Controller

DRAM

memory

System

Controller

DRAM

memory

Processor

Processor

DRAM

Data bus

Data

bus

PCI bus connections

(typically up to 5 devices)

Motherboard clock

speed

Local

SRAM

cache

Local

SRAM

cache

Bus

bridge

Bus

bridge

Processor clock

speed

Differing clock

speeds

IS

A

bus I

D

E

bus

U

SB bus

Figure 4.1

Local bus architecture