Biomedical Engineering Reference

In-Depth Information

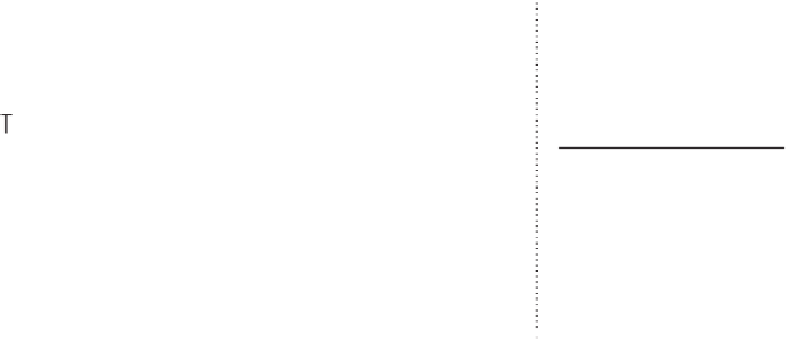

can be selected from the following settings: 1, 10, 20, 30, 40, 50, 60, 70, 80, 90, 100, 110,

120, 130, 140, or 150 ms using the thumbwheel switch. Figure 6.22 show the timing rela-

tionship of right-atrium, right-ventricle, and left-ventricular CENELEC signal generation.

When a physician programs a pacemaker to the patient's needs, the patient's heart is

usually monitored with a single-lead ECG. The cardiac simulator incorporates the simple

ECG signal generator circuit of Figure 6.23 to provide an output that can be monitored

with a standard single-lead ECG machine. An ECG signal is generated from digital values

stored in IC37, a PIC16C77 microcontroller, and output through the microcontroller's SPI

port to D/A converter IC34. R99 and R100 attenuate the output of IC34 to approximately

2 mV peak to peak. The P- and R-wave ECG signals are synchronized with the right-atrial

and right-ventricular CENELEC output signals.

In Chapter 8 we explain how pacemakers can use impedance signals to derive control infor-

mation based on the heart's contractile state. For the time being, su

ce it to say that as the

heart pumps, the volume of the blood pool around the electrodes changes. Since blood is more

conductive than is muscle tissue, these volume changes result in a varying electrical imped-

ance between the electrodes. The cardiac simulator incorporates a voltage-to-impedance con-

verter to simulate cardiac impedance signals. This circuit is based on an idea by Belusov

[1996] and was designed by Greg Martin, now a project manager at HyTronics. As shown in

Figure 6.24, IC36, an LTC1451 D/A converter, generates a voltage waveform that is stored in

the microcontroller's ROM in the same way as are the ECG and CENELEC signals. In this

case, however, the voltage output of the D/A is converted into an impedance signal.

This impedance waveform is synchronized with the left-ventricular CENELEC output sig-

nal. R79 sets the baseline impedance value (typically, 500

). IC35, a MAX038 sinusoidal

waveform generator, simulates the impedance variations caused by respiration. The fre-

quency of the respiratory component is set by R102. The intracardiac impedance and

respiration waveforms are summed into the inverting input of IC40A. The output of

IC40A, a summing, inverting ampli

Ω

fi

er circuit, is given by

1

V

.6

2

r

V

z

Right Atrial

Cenelec

Signal

Right Ventricular

Cenelec Signal

13ms

2ms

Left Ventricular

Cenelec Signal

Start

Fixed A-V Delay

of 100ms

Time Delay Set by

Thumb Wheel Switch

Figure 6.22

A typical “cardiac” cycle starts with generation of a right-atrial CENELEC signal followed by the right-ventricular CENELEC

signal. The delay from the start of the right-atrial signal to the beginning of the right-ventricular signal is fixed in the cardiac simulator at

100 ms. The left-ventricular signal starts after the right-ventricular signal with a programmable time delay.

Search WWH ::

Custom Search