Hardware Reference

In-Depth Information

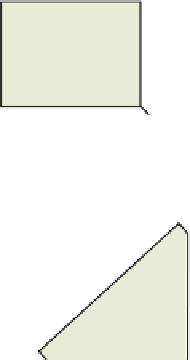

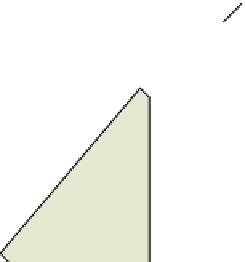

Cache model

Search in

the cache

Provoke

miss

Anotated SW code

Addresses

HW Platform model

Update

cache

Cache model

Annotated SW code

Provoke

miss

Addresses

Hit bit

checking

HW Platform model

Update

cache

Fig. 2.9

The underlying concept applied to reduce of cache modeling overhead. The idea is to

reduce the overhead by removing the function calls and searches done in the cache that are required

when a new line is required. Instead, a bit checking is integrated in the software code annotation.

Thus the cache model is only accessed at cache misses

containing instructions of different basic blocks are checked in all the blocks, so the

reduction is slightly reduced.

The second improvement is even more important for complex caches. In order

to avoid time-consuming

“tag”

searches, the dynamic search is replaced by a static

“bit checking”

solution. In the proposed model, a cache line is modeled as a structure

which includes the target set at which it may be allocated and a flag which determines

if a line is currently allocated in cache:

struct icache_line {

char num_set;

char hit;

}

The cache is modeled as a two-dimension array of pointers to cache line structures.

The dimensions of the array depend on the physical characteristics of the cache to be

considered (size, associativity and line size). All necessary methods for fetching or

replacing data are also provided with the model. The caching mechanism consists of

storing the addresses of the line structures in the array. An empty location in cache

is modeled as NULL value.

The struct for each cache line is declared statically inside the SW code as part of

the annotation, not in the cache model. This is done with the following line.

static icache_line line_124 = {0,0};

Search WWH ::

Custom Search