Hardware Reference

In-Depth Information

The frame rate requirements are not continuously updated but new requirements

are communicated only when the vehicle speed passes certain thresholds or when

another vehicle enters/exits the proximity areas. There is a threshold every 10 km/h

for the lateral cameras and every 20 km/h for the central camera.

We here recall from Chap. 5 that the RRM needs also application priorities to

decide which requirement should be relaxed when would be otherwise impossible

to solve the RRM problem matching all requirements given the limited amount of

system resources. The CSU communicates to the MPSoC platform also the priorities

of the multiple video streams together with the frame rate requirements. By default

the highest priorities are given to the central and left cameras. When a vehicle is in

proximity, then the lateral camera closer to the approaching vehicle and the central

camera get the highest priorities.

9.3

Platform Description

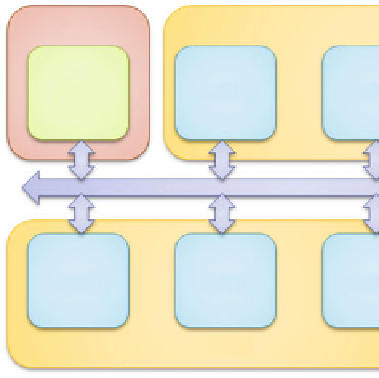

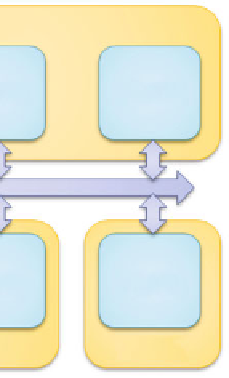

The industrial architecture studied is the 8-cores MPSoC shown in Fig.

9.4

. The

platform is composed of seven ADRES (coarse-grain Architecture for Dynamically

Reconfigurable Embedded System) cores [

5

] and one StrongARM. The ADRES core

is a power-efficient flexible computing element which combines a coarse-grain array

with a VLIW DSP. The MPEG4 application has been optimized for compilation for

the ADRES core in such a way that the data-flow loops can be efficiently accelerated

by exploiting the coarse-grain array for loop level parallelization. The potentialities

of the ADRES cores are fully exploited by executing the MPEG4 encoder instances

while the RRM is executed on the StrongARM processor. The on-chip interconnect

consists of a 32-bit wide Network-on-Chip with two switches.

RRM

MPEG4

Strong

ARM

ADRES

ADRES

ADRES

ADRES

ADRES

ADRES

ADRES

MPEG4

MPEG4

Fig. 9.4

Target MPSoC platform executing the RRM and the three MPEG4 encoder instances

Search WWH ::

Custom Search