Hardware Reference

In-Depth Information

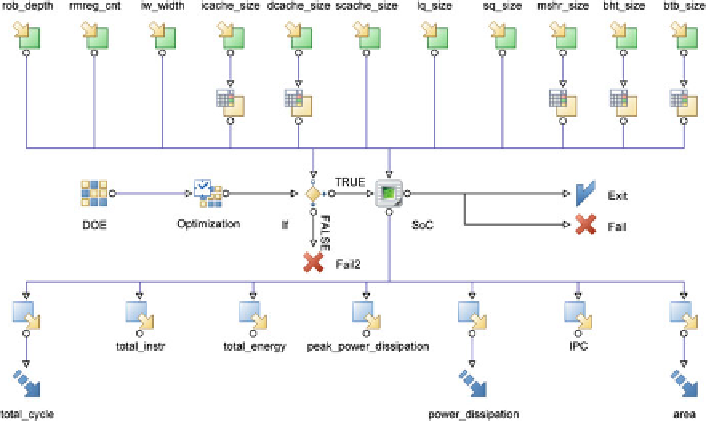

Fig. 8.1

The modeFRONTIER optimization workflow

The worklow specifies both a data path and a process path, which represent respec-

tively, the data flow for the evaluation of a design and the optimization execution

flow as described below.

The data path, which flows vertically from the top to the bottom, contains one

input node for each configuration parameter and one output node for each metric

produced by the simulator. In this optimization task there are eleven input nodes

and seven output nodes. The System-on-Chip node (labeled as SoC) represents the

interaction with the simulator, and takes care of the interface between the exploration

tool and the simulator, passing values for the configuration parameters and getting

back the values of the metrics as produced by the simulator. The three objectives to

be minimized are represented with the arrow nodes.

The process path, which flows horizontally from left to right, starts with the Design

of Experiments node (DoE), which generates the initial set of configurations to be

evaluated. The optimization node (Optimization) guides the exploration of the design

space using an optimization algorithm to generate the subsequent configurations that

will be evaluated based on the performance of previous evaluations. The conditional

node (If) passes only feasible designs for evaluation to the System-on-Chip node.

Successful executions of the simulator will generate a valid design (Exit), and errors

will generate failed designs (Fail).

8.2.3.2

Design of Experiments

The Design of Experiments (DoE) technique is used to generate the initial set of

designs for evaluation. The aim is to define a limited number of test runs that allow

to maximize the knowledge gained by eliminating redundant observations, in such a

Search WWH ::

Custom Search