Hardware Reference

In-Depth Information

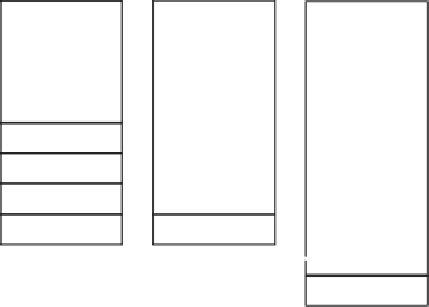

32-bit

Logical Space

32-bit

Physical Space

40-bit

Physical Space

00000000

00 00000000

P0/U0

(TLB)

3.5GB

Linear

Space

1TB

Linear

Space

7FFFFFFF

80000000

(2

32

-2

29

Bytes)

P1 ( PMB)

P2 (PMB)

P3 (TLB)

P4

(2

40

-2

29

Bytes)

E0000000

P4

FFFFFFFF

FF E0000000

FF FFFFFFFF

P4

Fig. 3.45

Example of logical and physical address spaces of SH-X4

continuously increasing and will soon exceed 2 GB even in an embedded system.

Therefore, we extended the number of physical address bits to 40 bits, which can

define 1-TB address space. The logical address space remained 32 bits, and the

programming model was not changed. Then the binary compatibility was main-

tained. The logical address space extension would require the costly 32-to-64-bit

extensions of register files, integer executions, branch operations, and so on.

Figure

3.45

illustrates an example of the extension. The 32-bit logical address

space is compatible to the predecessors of the SH-X4 in this example. The MMU

translates the logical address to a 32/40-bit physical address by TLB or privileged

mapping buffer (PMB) in 32/40-bit physical address mode, respectively. The TLB

translation is a well-known dynamic method, but the original PMB translation is a

static method to avoid exceptions possible for the TLB translation. Therefore, the

PMB page sizes are larger than that of the TLB in order to cover the PMB area

ef fi ciently.

The logical space is divided into five regions, and the attribute of each region can

be specified as user-mode accessible or inaccessible, translated by TLB or PMB,

and so on. In the example, the P0/U0 region is user-mode accessible and translated

by TLB, the P1 and P2 region are user-mode inaccessible and translated by PMB,

and the P3 region is user-mode inaccessible and translated by TLB. The P4 region

includes a control register area that is mapped on the bottom of physical space so

that the linear physical space is not divided by the control register area.

3.1.8.4

Data Transfer Unit

High-speed and efficient data transfer is one of the key features for multicore perfor-

mance. The SH-X4 core integrates a DTU for this purpose. A DMAC is conventional

hardware for the data transfer. However, the DTU has some advantage to the DMAC,

Search WWH ::

Custom Search