Hardware Reference

In-Depth Information

Fig. 3.43

Instruction

decoder of SH-X4

C0

C1

C2

C3

MUX

MUX

MUX

MUX

PD0

ID0

PD1

ID1

Prefix

Dec. 0

Prefix

Dec. 1

Normal

Dec. 0

Normal

Dec. 1

MUX

MUX

Output 0

Output 1

Table 3.11

Input patterns and selections

Input

Output

C0

C1

C2

C3

PD0

ID0

PD1

ID1

N

N

-

-

-

C0

-

C1

N

P

-

-

-

C0

C1

C2

P

-

N

-

C0

C1

-

C2

P

-

P

-

C0

C1

C2

C3

P

pre fi x,

N

normal, - arbitrary value

Dhrystone

v2.1

2.28

→

2.65 MIPS/MHz

116%

FFT

123%

FIR

134%

JPEG Encode

110%

0

50

100

(%)

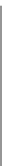

Fig. 3.44

Performance improvement ratio by pre fi x codes

improved by 23%, 34%, and 10%, respectively. On the other hand, area overhead of

the prefix code implementation was less than 2% of the SH-X4. This means the ISA

extension by the prefix codes enhanced both performance and efficiency.

3.1.8.3

Address-Space Extension

The 32-bit address can define an address space of 4 GB. The space consists of main

memory, on-chip memories, various IO spaces, and so on. Then the maximum linearly

addressed space is 2 GB for the main memory. However, the total memory size is

Search WWH ::

Custom Search