Hardware Reference

In-Depth Information

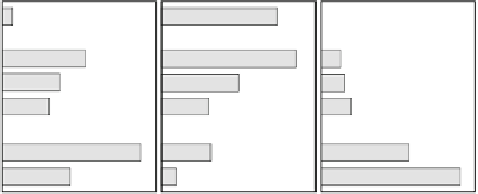

SH-3

SH-4

SH-X

1.00

1.00

1.00

x1.4

2.47

2.12

1.17

3.45

2.10

1.64

0123

Architectural

performance

0

1 2

Relative power

0

0.5

1.0

1.5

Architectural power-

performance ratio

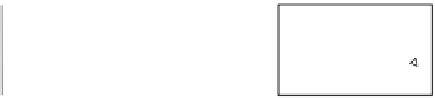

SH-3

60

600

100

3.30 V, 60 MHz

SH-4

1.95 V, 240 MHz

1.80 V, 166 MHz

1.50 V, 133 MHz

430

700

610

300

400

750

240

240

1000

SH-X

1.25 V, 400 MHz

1.00 V, 200 MHz

250

2880

720

360

80

4500

0

200 400 600

Performance

(MIPS)

0

200 400

Power

(mW)

600

0 2000 4000

Power-performance

Ratio (MIPS/W)

Fig. 3.18

Power ef fi ciency improvement of SH-4 and SH-X

same frequency of 200 MHz and by 1.4 times at the same supply voltage with

enhancing the performance by 1.4 times. These were architectural improvements,

and actual improvements were multiplied by the process porting.

3.1.4

Frequency and Ef fi ciency Enhancement of SH-X2

An SH-X2 was developed as the second-generation core and achieved performance

of 1,440 MIPS at 800 MHz using a 90-nm process. The low-power version achieved

the power efficiency of 6,000 MIPS/W. The performance and efficiency are greatly

enhanced from the SH-X by both the architecture and microarchitecture tuning and

the process porting.

3.1.4.1

Frequency Enhancement of SH-X2

According to the SH-X analyzing, the ID stage was the most critical timing part,

and the branch acceleration successfully reduced the branch penalty. Therefore, we

added the third instruction fetch stage (I3) to the SH-X2 pipeline to relax the ID

stage timing. The cycle performance degradation was negligible small by the suc-

cessful branch architecture, and the SH-X2 achieved the same cycle performance of

1.8 MIPS/MHz as the SH-X.

Search WWH ::

Custom Search