Hardware Reference

In-Depth Information

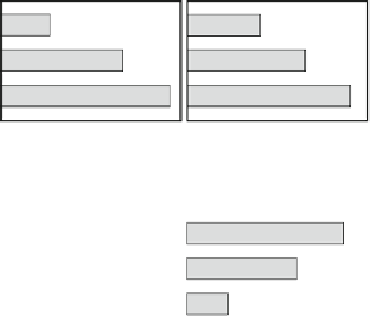

SH-3

1.00

1.00

1.00

SH-4

SH-X

2.47

1.63

1.52

3.45

2.26

1.53

0

1

2

3

0

1

2

0

0.5 1.0 1.5

Architectural area-

performance ratio

Architectural

performance

Relative area

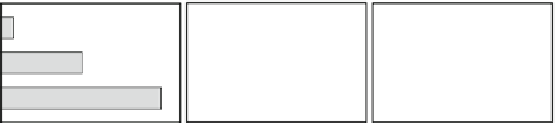

SH-3

60

7.0

8.6

SH-4

SH-X

361

4.9

74

720

1.8

400

0

200

400

600

Performance

(MIPS)

0

1

2

3

4

5

6

7

0 100

200 400

Area-performance

Ratio (MIPS/mm

2

)

300

Area (mm

2

)

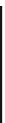

Fig. 3.17

Area ef fi ciency improvement of SH-4 and SH-X

The cycle performance was decreased by 18% to 1.47 MIPS/MHz with adopting a

conventional seven-stage superpipeline to the SH-4. Branch prediction, out-of-order

branch issue, store buffer, and delayed execution improve the cycle performance by

23% and recover the 1.8 MIPS/MHz. Since 1.4 times high operating frequency was

achieved by the superpipeline architecture, the architectural performance was also

1.4 times as high as that of the SH-4. The actual performance was 720 MIPS at

400 MHz in a 0.13-mm process and improved by two times from the SH-4 in a 0.25-

mm process. The improvement by each method is shown in Fig.

3.16

.

Figures

3.17

and

3.18

show the area and power efficiency improvements, respec-

tively. Upper three graphs of both the figures show architectural performance, rela-

tive area/power, and architectural area-/power-performance ratio. Lower three

graphs show actual performance, area/power, and area-/power-performance ratio.

The area of the SH-X core was 1.8 mm

2

in a 0.13-mm process, and the area of the

SH-4 was estimated as 1.3 mm

2

if it was ported to a 0.13-mm process. Therefore, the

relative area of the SH-X was 1.4 times as much as that of the SH-4 and 2.26 times

as much as the SH-3. Then the architectural area efficiency of the SH-X was nearly

equal to that of the SH-4 and 1.53 times as high as the SH-3. The actual area

efficiency of the SH-X reached 400 MIPS/mm

2

, which was 8.5 times as high as the

74 MIPS/mm

2

of the SH-4.

SH-4 was estimated to achieve 200 MHz, 360 MIPS with 140 mW at 1.15 V, and

280 MHz, 504 MIPS with 240 mW at 1.25 V. The power efficiencies were 2,500

and 2,100 MIPS/W, respectively. On the other hand, SH-X achieved 200 MHz,

360 MIPS with 80 mW at 1.0 V, and 400 MHz, 720 MIPS with 250 mW at 1.25 V.

The power efficiencies were 4,500 and 2,880 MIPS/W, respectively. As a result,

the power efficiency of the SH-X improved by 1.8 times from that of the SH-4 at the

Search WWH ::

Custom Search