Hardware Reference

In-Depth Information

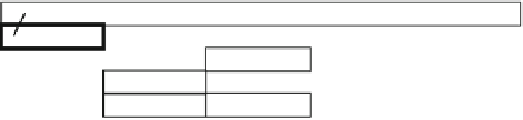

IF

Early Branch

Branch

Instruction Fetch

Instruction Decoding

FPU Instruction Decoding

ID

EX

MA

WB

Execution

Address

Sign

FPU

Execution

& WB

Load/Store

-

-

WB

WB

WB

BR

INT

LS

FE

Fig. 3.1

Pipeline structure of SH-4

3.1.2.4

Pipeline Structure of Asymmetric Superscalar Architecture

Figure

3.1

illustrates the pipeline structure to realize the asymmetric superscalar

architecture described above. The pipeline is five stages of instruction fetch (IF),

instruction decoding (ID), instruction execution (EX), memory access (MA), and

write-back (WB).

Two consecutive instructions of 32 bits are fetched every cycle at the IF stage to

sustain the two-way superscalar issue and provided to the input latch of the ID

stage. The fetched instructions are stored in an instruction queue (IQ), when the

latch is occupied by the instructions suspended to be issued. The instruction fetch is

issued after checking the emptiness of either the input latch or the IQ to avoid dis-

carding the fetched instructions.

At the ID stage, instruction decoders decode the two instructions at the input latch,

judge the group, assign pipelines, read registers as source operands, forward a operand

value if it is available but not stored in a register yet, judge issuable immediately or

not, and provide instruction execution information to the following stages. Further,

BR pipeline starts a branch processing of a BR-group instruction. The details of the

branch processing are described in the next section.

The INT, LS, BR, and FE pipelines are assigned to an instruction of the INT, LS,

BR, and FE groups, respectively. The second instruction of the two simultaneously

decoded ones is not issued if the pipeline to be assigned is occupied, kept at the

input latch, and decoded again at the next cycle. A BO group instruction is assigned

to the LS pipeline if the other instruction simultaneously decoded is the INT group;

otherwise, it is assigned to the INT pipeline, except both the instructions are in the

BO group. In this case, they are assigned to the INT and LS pipelines. The NS

instruction is assigned to a proper pipeline or pipelines if it is the first instruction;

otherwise, it is kept at the input latch and decoded again at the next cycle.

The issue possibility is judged by checking the operand value availability in par-

allel with the execution pipeline assignment. An operand is immediate value or

register value, and the immediate value is always available. Therefore, the register

value availability is checked for the judgment. The register value is defined by some

instruction and used by a following instruction. A write-after-read register conflict,

a true dependency in other words, occurs if the distance of the defining and using

instructions is less than the latency of the defining instruction, and the defined reg-

ister value is not available until the distance becomes equal or more than the latency.

Search WWH ::

Custom Search