Hardware Reference

In-Depth Information

Table 3.2

Categories of SH-4 instructions

INT

LS

BR

NS

MOV imm, Rn,

MOVA, MOVT

ADD, ADDC, ADDV

SUB, SUBC, SUBV

DIV0U, DIV0S, DIV1

DT, NEG, NEGC

EXTU, EXTS

AND Rm, Rn, AND imm, R0

OR Rm, Rn, OR imm, R0

XOR Rm, Rn, XOR imm, R0

ROTL, ROTR

ROTCL, ROTCR

SHAL, SHAR,

SHLL, SHLR

SHLL2, SHLR2

SHLL8, SHLR8

SHLL16, SHLR16

SHAD, SHLD

NOT, SWAP, XTRCT

MOV (load/store)

MOVCA

OCBI, PREF

FMOV

FLDS, FSTS

FLDI0, FLDI1

FABS, FNEG

LDS Rm, FPUL

STS FPUL, Rn

BRA

BSR

BT

BF

BT/S

BF/S

MUL, MULU, MULS

DMULU, DMULS

MAC, CLRMAC

AND imm, @(R0,GBR)

OR imm, @(R0,GBR)

XOR imm, @(R0,GBR)

TST imm, @(R0,GBR)

TAS, BRAF, BSRF

JMP, JSR, RTS

CLRS, SETS, SLEEP

LDC, STC

LDS (except FPUL)

STS (except FPUL)

LDTLB, TRAPA

FE

FADD

FSUB

FMUL

FDIV

FSQRT

FCMP

FLOAT

FTRC

FCNVSD

FCNVDS

FMAC

FIPR

FTRV

BO

MOV Rm, Rn

CMP

TST imm, R0

TST Rm, Rn

CLRT

SETT

NOP

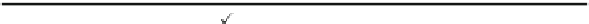

Table 3.3

Simu

ltaneous issue of instructions

Second instruction category

BO

INT

LS

BR

FE

NS

First

instruction

category

BO

INT

LS

BR

FE

NS

The SH ISA supports floating-point sign-negation and absolute-value (FNEG

and FABS) instructions. Although these instructions seemed to fit the FE group,

they were categorized to the LS group. Their operations were simple enough to

execute at the LS pipeline, and the combination of another arithmetic instruction

became a useful operation. For example, the FNEG and floating-point multiply-

accumulate (FMAC) instructions became a multiply-and-subtract operation.

Table

3.2

summarizes the categories of the SH-4 instructions, and Table

3.3

shows the ability of simultaneous issue of two instructions. As an asymmetric super-

scalar processor, each pipeline for the INT, LS, BR, or FE group is one, and the

simultaneous issue is limited to a pair of different group instructions, except for a

pair of the BO group instructions, which can be issued simultaneously using both

the INT and LS pipelines. An NS group instruction cannot be issued with another

instruction.

Search WWH ::

Custom Search