Hardware Reference

In-Depth Information

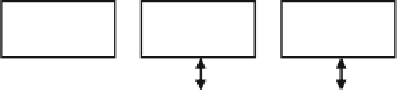

DMAC

MX core

CPU #0

CPU #1

On-Chip Bus

SDRAM

I/F

SDRAM

Fig. 6.12

Example of SoC system architecture including MX core

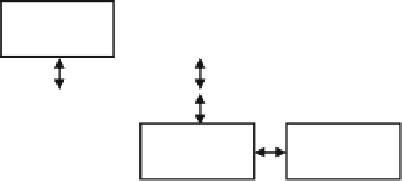

Semantic Information

“Count”

“Run”

“Congestion”

Tracking Information

S-T MRF

Fig. 6.13

Spatiotemporal Markov random fi eld model

6.2.2

MX Application

The MX core is an embedded processor core in SoCs. Therefore, a suitable SoC

system architecture needs to be designed in order to extract the total performance of

the MX core. A heterogeneous multicore system architecture is a promising option

for real-time image recognition applications.

Figure

6.12

schematically shows an example of an SoC system architecture,

which is a heterogeneous multicore structure consisting of multiple CPUs, the MX

core, and required peripheral IPs. It also includes the DMA controller that controls

the data transfers between the MX core and the external memory. With this archi-

tecture, high-performance image processing and recognition applications can be

achieved by optimizing the software architecture. Hereafter, an application example

and its implementations on this system are shown [

7

] .

Figure

6.13

shows an application example of the MX core using the spatiotem-

poral Markov random field model (S-T MRF) [

8

]. The S-T MRF is a powerful

tracking algorithm for camera applications such as traffic-sensing cameras and sur-

veillance cameras. The algorithm has the following features:

•

It is independent of object shapes.

•

It can deal with occluded objects.

The software layers are also shown in Fig.

6.13

. The bottom layer is the S-T

MRF layer, which extracts the tracking information and passes it to the upper layer.

The upper layer is the semantic layer, which interprets the tracking information as

traffic conditions, for example, congested or clear.

Search WWH ::

Custom Search