Hardware Reference

In-Depth Information

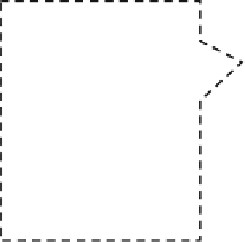

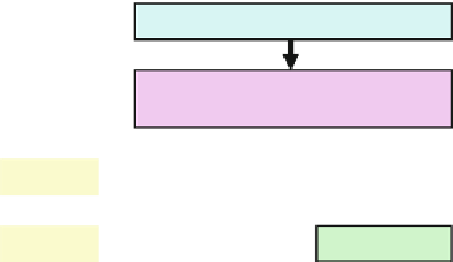

void main (void)

{

1.

Controller

CPU

ADD

Instruction

Memory

SUB

MAC

// Library I/F

MX ADD ( );

MX SUB ( );

:

2.

}

SIMD Data-path

3.

B[0]

+A[0]

B[1]

+A[1]

B[2]

+A[2]

B[3]

+A[3]

PE

PE

PE

PE

A[0]

A[1]

A[2]

A[3]

1. Calling the MX function.

2. Issuing the SIMD instruction.

3. SIMD parallel processing.

Fig. 6.10

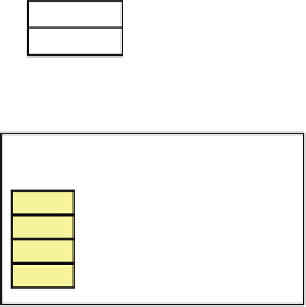

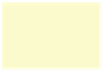

MX microcode library

User Application

API

Application

Specific

Library

Application

Specific

functions

(Filters, FFT,

)

Image/Signal Processing Library

Microcode

Basic Library

Arithmetic/

Logical

functions

(ADD, AND,

)

Hardware

CPU

MX core

Fig. 6.11

Software interface of MX core

normally employs a CPU as a general-purpose controller. The CPU calls MX

microcode functions in the main program written in C language. The MX controller

decodes microcode functions called by the CPU and generates control signals for

the SIMD data path. In the data path, all PEs operate simultaneously by these control

signals. Overall, such simple programming realizes massively parallel operations

on the MX core [

5,

6

] .

The software interface of the MX core is shown in Fig.

6.11

. The CPU and MX

core are employed in the hardware layer. The primitive microcode library is imple-

mented to support the simple arithmetic and logical operations. In addition, an

application-specific library layer, for example, an image and signal processing

library, is prepared in the higher layer. This library layer offers the optimum codes

for the MX core and CPU, and it conceals the unique hardware structure of the MX

core. Therefore, users only need to call the simple APIs of the specific library and

do not have to worry about the super parallel structure of the MX core.

Search WWH ::

Custom Search