Hardware Reference

In-Depth Information

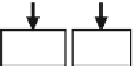

Real time control

applications

IT applications

PPC

error

handler

INT

handler

INT

handler

RTOS

Versatile OS

LCPG

INTC

CPU #0

CPU #1

CPU #2

CPU #3

DMAC

PCIe

SHPB

PPC

PPC

PPC

Internal system bus

PPC

PPC

PPC

WDT

TMU

HAC

Ether

USB

DU

HPB

LBSC

DBSC

Peripheral bus

CPG

GPIO

HSPI

SCIF

I2C

SSI

SDIF

ROM

RAM

Fig. 5.13

Implementation of the physical partitioning controller

Table 5.15

Number of access checklist (ACL) entries for each physical partitioning controller

No. of ACLs

needed

No. of ACLs

implemented

PPC

Initiator

Target

LBSC-PPC

2 CPU cores

2 ROM areas

2

4

DBSC-PPC

2 CPU cores 9

initiator modules

2 RAM areas allocated

to a domain 1 RAM

area shared by

domains

11 + 11

32

SHPB-PPC

2 CPU cores

4 Target modules

4

8

HPB-PPC

2 CPU cores

27 Target modules

27

32

DMAC-PPC

2 CPU cores

2 Target modules

2

4

PCI-PPC

2 CPU cores

3 Target modules

3

4

and ACLs. Table

5.15

lists the number of ACL entries of each PPC. For SHPB-

PPC, HPB-PPC, DMAC-PPC, and PCI-PPC, the initiators are CPU cores, and the

targets are modules connected on the bus-target modules; therefore, an ACL entry

is needed for each target to authenticate an access from the CPU cores of the

domain. For LBSC-PPC, CPU cores gain access to two ROM areas that are each

allocated to a domain; therefore, LBSC-PPC needs an ACL entry for each ROM

Search WWH ::

Custom Search