Hardware Reference

In-Depth Information

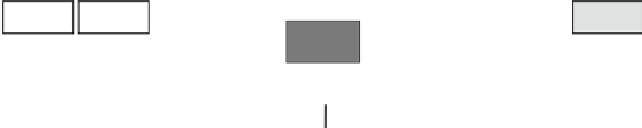

RT domain

IT domain

CPU #0

CPU #1

CPU #2

CPU #3

Timer

INTC

Timer

INTC

Partition

Controller

GPIO

SCIF

DMAC

RAM Con

SCIF

DMAC

DU

PCI

Dev

RAM

Display

Net

Fig. 5.8

Physical partitioning

Resetting the domain and rebooting its operating system without letting the other

domains observe any of the failure's effects

Lowering system performance overhead to less than 5% to implement fault

isolation

5.2.4

Partitioning of Multicore Processor Systems

Partitioning techniques with hardware support fall into two categories: physical par-

titioning and logical partitioning [

12

] .

5.2.4.1

Physical Partitioning

With physical partitioning, each domain uses dedicated processor resources. In the

multidomain system in Fig.

5.8

, system designers allocate each CPU core and each

group of channels in multichannel devices—DMA controllers (DMAC), timer units

(TMU), and serial communication interfaces (SCIF)—and other devices, such as

the display unit (DU), PCI, and general-purpose I/O (GPIO), to one of the domains.

Each allocated resource is physically distinct from the resources used by the other

domain. Although the domains share the on-chip system bus, each transaction is

dedicated to a domain. This prevents the other domain from affecting transactions

that relate to issues other than bandwidth.

In physical partitioning, each partition's configuration—that is, the resources

assigned to a domain—is controlled in the hardware (such as the partition con-

troller in Fig.

5.8

), because physical partitioning does not require sophisticated

algorithms to schedule and manage resources. When the system boots up, the

partition controller sets up the hardware resources to use in a partition according

Search WWH ::

Custom Search